基于FPGA的寬帶數(shù)字信道化接收機(jī)的設(shè)計(jì)

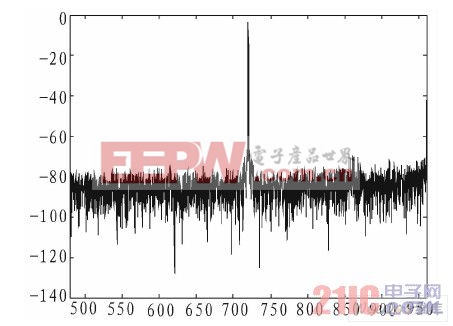

實(shí)驗(yàn)一:輸入信號頻率為由信號源Agilent 83752A產(chǎn)生的正弦波,頻率為720 MHz,幅度為-1 dBFS,采樣頻率為960MHz,從FPGA中導(dǎo)出采樣數(shù)據(jù)作8 k點(diǎn)的FFT,得信號頻譜如圖8所示。

圖8 A/D輸出720MHZ信號頻譜圖

經(jīng)計(jì)算得,信噪比RSN為47.5 dB,信號噪聲失真比SINAD為46.3 dB,有效位數(shù)ENOB為7.4 bits,無雜散動態(tài)范圍SFDR為59 dBc。

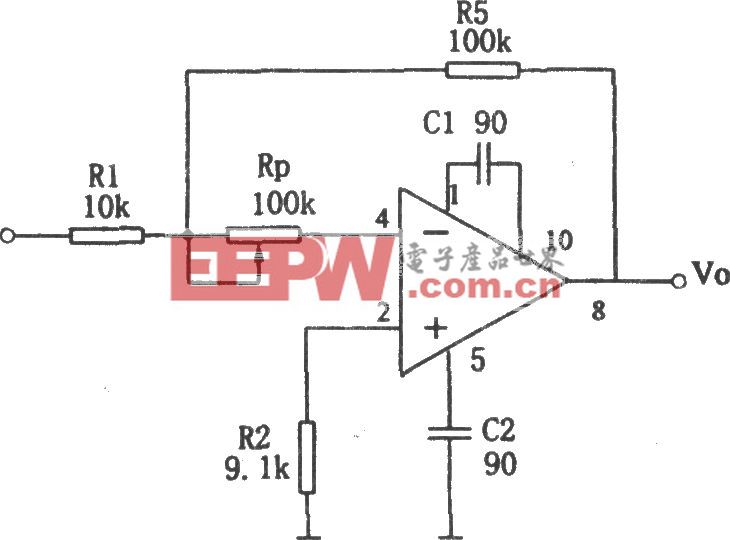

實(shí)驗(yàn)二:用Agilent的E4438C矢量信號發(fā)生器作為中頻輸入,輸入載頻為725 MHz,PRI=10μs,PW=2μs的脈沖信號測試結(jié)果如圖9所示。圖9中第一行表示輸入信號經(jīng)過LVDS降速后的輸出波形,中間15行表示15個(gè)信道包絡(luò)脈沖輸出,倒數(shù)第二行表示有包絡(luò)脈沖輸出的那一路輸出載頻碼,最后一行表示有包絡(luò)脈沖輸出的那一路輸出的相位差碼。

圖9 輸出界面

由以上的分析可知,載頻為725 MHz信號應(yīng)該出現(xiàn)在705~735 MHz的第9信道上,輸出載頻碼為725-480=245,DSP寫入校正編碼使輸出的相位差碼為0。由圖9可看出,只有第9信道有包絡(luò)脈沖輸出,輸出載頻碼為245,輸出的相位差碼為0,這與理論結(jié)果一致。

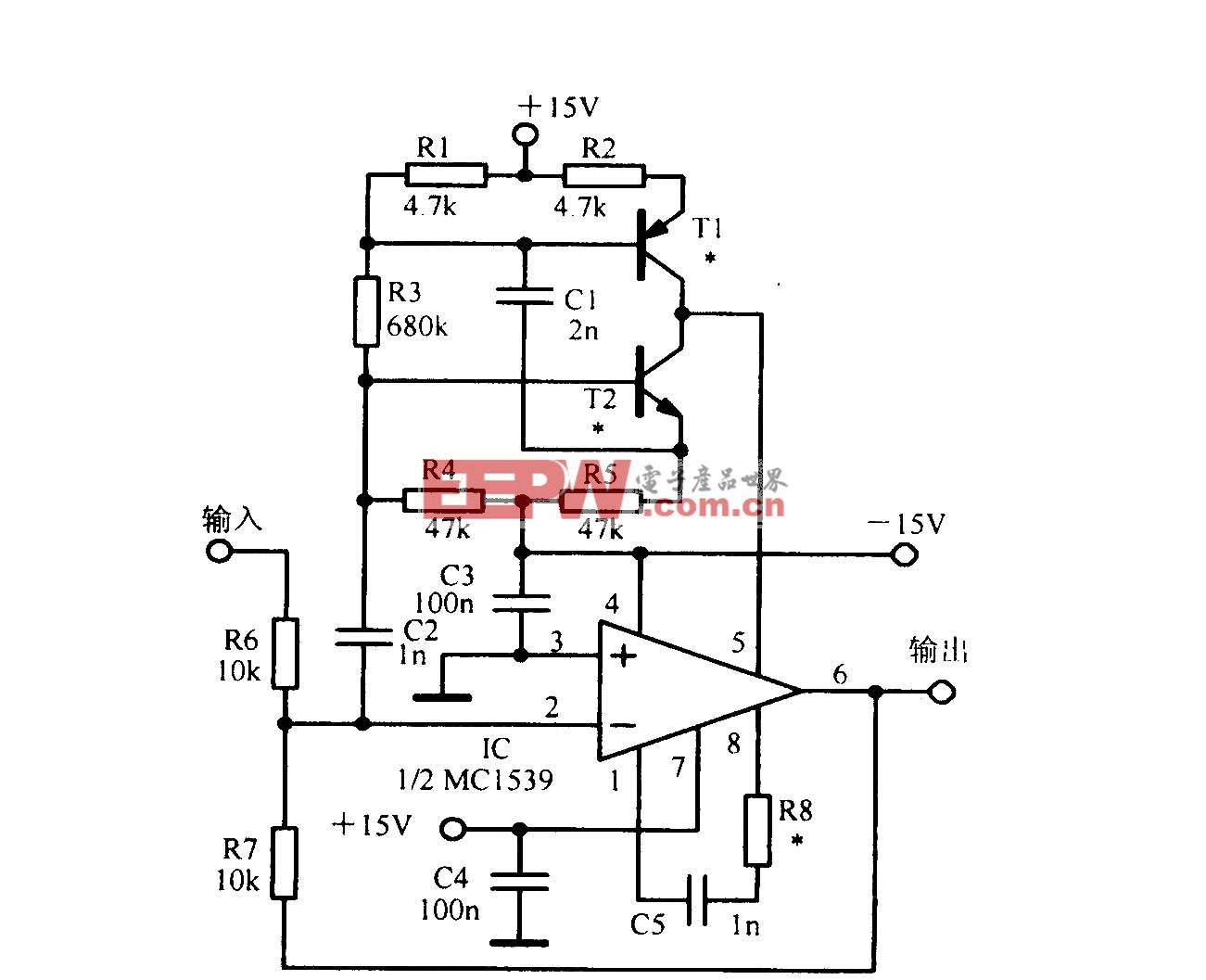

實(shí)驗(yàn)三:用Agilent的E4438C矢量信號發(fā)生器作為中頻輸入,輸入載頻為725 MHz,PRI=10μs,PW=2μs的脈沖信號。用示波器同時(shí)采集輸入中頻脈沖信號和輸出的信號包絡(luò)脈沖,可得信號載頻碼和相位差碼輸出延遲時(shí)間,即整個(gè)系統(tǒng)延遲時(shí)間測試結(jié)果如圖10所示。上邊的一條線為輸入的中頻脈沖信號,下邊的一條線為輸出的信號包絡(luò)脈沖,由圖10可以看出系統(tǒng)延遲時(shí)間小于1.3μs,保證了系統(tǒng)的實(shí)時(shí)處理。

圖10 系統(tǒng)延遲時(shí)間

評論