CPLD的串口電路設計

一、硬件電路設計

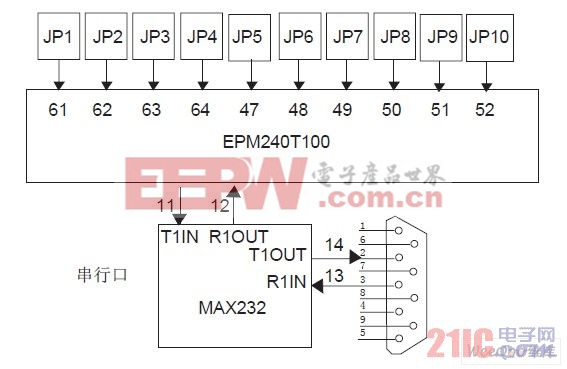

本文引用地址:http://www.104case.com/article/190020.htm本文選用CPLD 是ALTERA 公司的EPM240T100,結合MAX232 接口芯片進行串口通信設計,框圖如下圖1 所示。

二、VHDL程序模塊設計及描述

使用VHDL 對CPLD 進行編程,設計3 個模塊,波特率發生模塊,接收器,發送器。

1. 波特率發生模塊

波特率發生器實際是一個分頻器,如前所述,本文設計的波特率為19.2kb/ 秒,設計使用的時鐘頻率為10MHz,所以計數器進行計數時計數到260進行翻轉。

程序如下(關鍵部分保留,非必要部分用……代替):

……

ENTITY uart IS

GENERIC(d_len:INteGER:=8);

PORT (

f10MHz:IN STD_LOGIC;-- 系統時鐘

reset:IN STD_LOGIC;-- 復位信號

rxd:IN STD_LOGIC; -- 串行接收

txd:OUT STD_LOGIC;-- 串行發送

);

END uart;

ARCHITECTURE behav of uart IS

……

BEGIN

rxds=rxd;

PROCESS(f10MHz,reset)

-- 設置波特率發生器 19200kb/s

VARIABLE clk19200hz: STD_LOGIC;

VARIABLE count:INTEGER RANGE 0 TO 260;

BEGIN

IF reset='0' THEN

count:=0;

clk19200hz:='0';

ELSIF f10MHz'EVENT AND f10MHz='1' THEN

IF count=260 THEN

count:=0;clk19200hz:= NOT clk19200hz;

ELSE

count:=count+1;

END IF;

END IF;

baud_rate=clk19200hz;

END PROCESS;

分頻器相關文章:分頻器原理

評論