基于FPGA的寬帶數字信道化接收機的設計

現代電磁信號環境越來越復雜密集,要求電子戰接收機必須具有很寬的處理帶寬、高靈敏度、大動態范圍、多信號并行處理和大量信息實時處理的能力。而數字信道化接收機不僅可以較好地滿足上述要求,還可實現監視信道內信號的全概率截獲。

本文引用地址:http://www.104case.com/article/190021.htm數字信道化過程是寬帶數字接收機的核心,目前廣泛采用基于多相濾波的數字信道化結構。這種結構先用高速的模數轉換器(A/D)進行數據采樣,得到的高速數據流經抽取降低數據速率后進入多相濾波器組,該濾波器組是由一個原型濾波器調制到多個支路。現場可編程門陣列(FPGA)中豐富的乘法器、鎖存器及數字信號處理算法IP核等資源,可以非常靈活地實現寬帶數字信道化接收處理算法。本文采用基于多相濾波器的結構實現了一種高效高速的寬帶數字信道化接收機,并在Altera公司的EP3SE110F1152C4上綜合實現,輸出載頻、相位信息。

1 信道化接收機的基礎理論

1.1 信道劃分

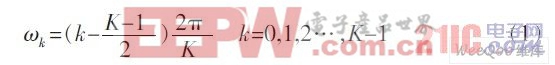

為建立實信號多信道接收機的數學模型,首先,對實信號的數字譜作如下信道劃分:

式(1)中,ωk為第k信道的歸一化中心角頻率;K為劃分信道數。圖1給出對應k=8時,實信道的頻譜分配情況。需要指出的是由于實信號的頻譜是對稱的,所以只有4個獨立的信道。

圖1 實信號的信道劃分示意圖

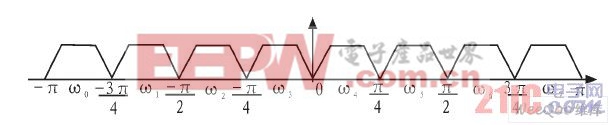

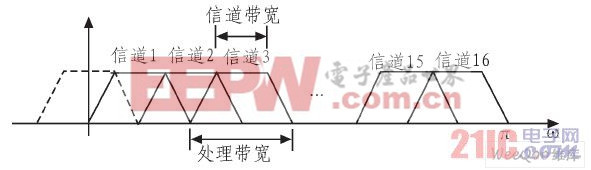

采用上述方法進行信道劃分有些頻點無法識別,為確保整個覆蓋帶寬內無盲區,信道的劃分選擇相鄰信道50%交疊,即擴大每個信道的處理帶寬,如圖2所示。

圖2 50%交疊的信道劃分示意圖

1. 2 多相濾波器組結構

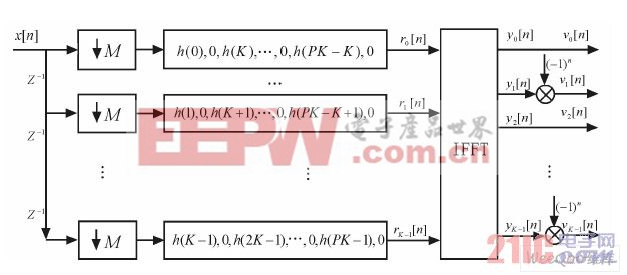

本文采用高速高效數字信道化結構完成信道化接收,其數學模型如圖3所示。

圖3 高速高效數字信道化接收機結構圖

圖3中K為系統劃分的信道數,M為每個信道的抽取倍數且K=FM。H(n)為原型低通濾波器的單位沖擊響應,K個帶通濾波器都是通過該原型濾波器調制生成的,即均勻濾波器組的多相濾波分量。

評論