基于CPLD及DDS的正交信號源濾波器的設計

3.2 CPLD模塊

該模塊通過一個4引腳的工業標準JTAG接口在系統編程(ISP),并且在編程過程中僅需5.0 V單電壓供電。編程過程中,I/O引腳處于三態并被上拉,以消除板上沖突。上拉阻值為1 kΩ。因為該器件是在線編程的,為了便于調試,所以把下載口直接做在電路板上。考慮到電源為自制的穩壓電源,CPLD受電源紋波干擾影響較大,所以在每個器件旁都加有去耦電容。

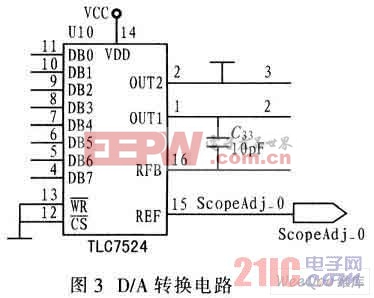

3.3 D/A轉換及幅度控制

D/A轉換采用TI公司的TLC7524,該器件轉換速度可達10 M,幅度控制D/A轉換采用MAX518,該器件是I2C總線的雙D/A轉換器,只需很少的端口線就可實現兩路幅度的控制,大大節省單片機的端口。圖3給出D/A轉換電路。

3.4 后級處理模塊

低通濾波器對階梯正弦波進行傅里葉分析。其中若一周期采樣點數為N,則其高次諧波能量主要集中在輸出頻率的(N±1)倍頻上,其幅值為基頻的 1/(N±1)。低通濾波可以平滑其臺階。另外還需濾除由DAC0832和TCL7524產生的1MHz和10 MHz的高頻分量。因此根據設計的要求(輸出最大頻率為250 kHz,為了保證250 kHz頻帶內輸出幅度平坦,又要盡可能抑制諧波和高頻分量,綜合考慮選用寬帶運放LF351,用EWB仿真表明:截止頻率為1 MHz~250 kHz以內幅度平坦。為了保證穩幅輸出,選用AD817。該器件是一種低功耗、高速、寬帶運算放大器,具有很強的大電流驅動能力。實際電路測量表明:當負載為100 Ω,輸出峰-峰值為10 V時,其帶寬大于500 kHz,幅度變化小于±1%。

4 軟件設計

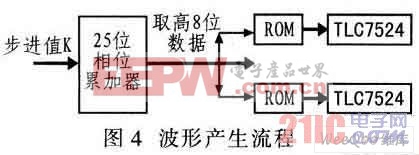

4.1 波形發生

在CPLD內設置25位相位累加器,高9位為ROM地址,低16 位為產生精確的讀ROM的點與點之間的時間間隔而設置的累加寄存器,即:單片機送一頻率控制字,由低16位寄存器每個時鐘都累加這個值,累加到低16位溢出,然后ROM的地址加1。ROM內的每個地址的數據表示當前波形的幅度,然后連續讀出數據并被平滑濾波后得出平滑、穩定的波形。波形產生流程如圖4所示。

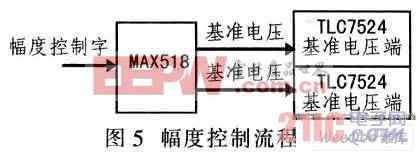

4.2 幅度控制

系統的幅度控制由MAX518完成,利用其內部電阻網絡實現數字電位器功能,輸出電壓作為TLC7524的基準電壓。圖5為幅度控制流程。

評論