基于FPGA的可配置FFT_IFFT處理器的設計與實現

2.4 乒乓RAM設計

為了滿足無線移動通信要求,實現對連續數據流和突發數據流的處理,本文設計的FFT/IFFT處理器采用了輸入、輸出雙乒乓結構,保證了系統高吞吐率的要求。設計共使用4組RAM(RAM0~RAM3),每組RAM劃分為4塊存儲器。輸入數據寫入RAM0組中的4塊存儲器,寫完后開始寫入RAM1,與此同時,從RAM0組中讀出數據送入蝶形單元進行計算,其結果按照同址計算規則寫回相應的地址,直到M級蝶形運算完成后,最終的計算結果寫入RAM2。RAM2寫滿后,即可從RAM2讀出計算結果,同時RAM1組中的數據將被讀出送入蝶形單元進行運算,其運算結果按照同址運算規律送回RAM1存儲,M級蝶形運算完成后,最終結果寫入RAM3組,RAM3寫滿后即可從中讀出運算結果。

2.5 無沖突并行地址設計[4]

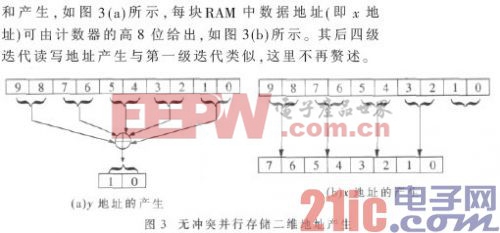

4路并行數據處理結構需要保證每次讀取的一組數據分別存儲在不同的RAM中,否則在數據讀取時會產生地址沖突[5]。本設計中RAM地址采用二維地址,其中地址x表示每塊RAM中數據地址,y表示數據來自RAM塊的標號。

3 FPGA實現及測試分析

本文FFT/IFFT處理器采用Verilg硬件語言描述,在Mentor公司的Modelsim仿真平臺上進行了RTL功能仿真及時序仿真,其結果與Matlab仿真結果進行比較顯示正確。處理器采用了Xilinx 公司Virtex-Ⅱ xc22v500 芯片進行了驗證,在SMIC COMS 0.18 ?滋m工藝下對設計的處理器進行了綜合仿真。結果顯示:完成64點16 bit符號數復數FFT運算只需要50個時鐘周期,完成256點FFT運算需要256個時鐘周期,最大時鐘頻率可以達到167 MHz,處理器的單元核心面積為1.4 mm2。設計完全滿足了無線移動手持終端設備高速小面積的設計要求。

p2p機相關文章:p2p原理

評論