京微雅格重磅之作―新版FPGA/CAP設計套件Primace5

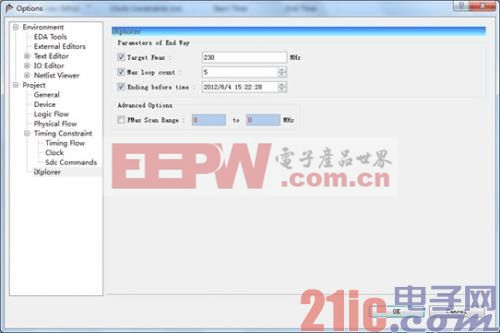

時序收斂工具iXplorer

配合新型的自動尋找最佳實現的優化工具iXplorer,用戶可以極大的加速設計時序收斂過程。

圖5:iXplorer配置界面

Primace5.0對iXplorer進行了多項重要改進。首先,引入了支持并行執行流程的新一代流程控制引擎,充分的利用了主流多核系統的計算資源。其次,新開發的新型fMAX掃描算法Range-Scan,在充分利用了并行計算優勢的基礎上,可以智能掃描時序約束(目前主要是時鐘頻率約束),用最短的時間尋找不同時序約束下設計實現的最佳fMAX。此外,iXplorer支持多種掃描結束條件,方便用戶在多種需求下的靈活使用。最后,當用戶得到最佳fMAX結果后,iXplorer提供了便捷的方式讓用戶把相應的約束條件設置到用戶環境,從而可以得到相應的結果。

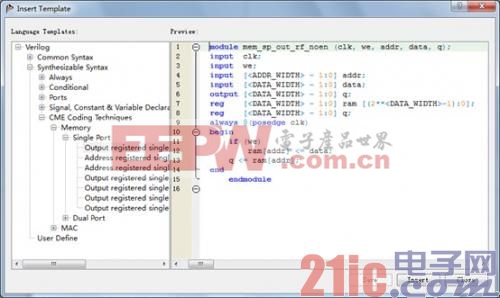

RTL模板

為了方便用戶準確描述設計,改善RTL 代碼質量,Primace5.0新增了RTL Template功能,其中包括了常用的Verilog設計元素。通過使用RTL Template,用戶可以方便快捷的在設計中插入經過Primace軟件驗證的RTL代碼,簡化了用戶設計輸入過程并提高了設計代碼質量。目前Primace RTL Template主要支持了以下幾類設計元素:

通用語法(注釋,編譯器控制語法等)

可綜合語法(目前僅支持Verilog可綜合子集,以及Memory, Multiplier等可以自動推斷的代碼模式)

用戶自定義模板

圖6:RTL模板瀏覽界面

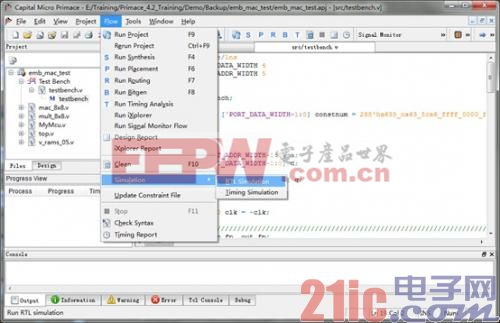

SoC仿真與時序仿真

Primace5.0還第一次完整支持了8051MCU的SoC仿真,以及時序仿真(Timing Simulation)。首先,通過簡明易用的工程文件管理,方便用戶對設計文件和測試平臺文件進行編輯和管理;其次,引入了對8051MCU的SoC仿真支持,完全改變了過去調試8051MCU需要依賴第三方工具的調試模式,大大提升了用戶SoC設計的調試效率,加快了用戶SoC設計的整個驗證和調試流程。最后,引入了對時序仿真的支持,為解決用戶設計中遇到的時序收斂問題提供了一條全新的分析和調試的途徑,加快了用戶設計時序收斂的過程。

圖7:仿真調用界面

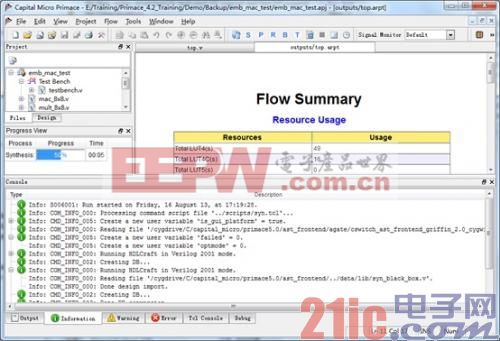

流程及信息提示

相對上一代版本,新一代Primace顯著改進了用戶信息提示以及流程的穩定性。Primace 5.0對用戶設計實現中各個階段的流程信息重新進行了劃分,將所有信息分為4類:命令信息,執行信息,警告信息和錯誤信息,對每一類信息逐條進行了編號,并引入了同類信息的折疊顯示,方便用戶通過流程信息了解設計實現的實時情況。此外,良好的用戶信息分類和顯示也提升了流程日志的可用性,進一步方便用戶了解設計實現的過程。

圖8:信息提示界面

評論