京微雅格重磅之作―新版FPGA/CAP設計套件Primace5

簡介

本文引用地址:http://www.104case.com/article/189497.htm作為國內唯一一家具有完全自主知識產權的FPGA與可配置應用平臺CAP(Configurable Application Platform)產品供應商,京微雅格一直在快節奏的改進與產品配套的軟件開發環境。最近,新一代FPGA/CAP設計套件Primace5.0正式發布了。Primace5.0完整的支持了基于時序驅動的布局布線實現流程(Timing-Driven PlacementRouting Flow),提高了布局布線的成功率,減少了設計與驗證時間。此外,Primace5.0還配套改進了Synopsys SDC兼容的設計約束輸入界面, 方便用戶更加準確高效的輸入時序約束。配合新型的自動尋找最佳實現的優化工具iXplorer,Primace 5.0可以極大的加速用戶設計時序收斂過程。為了方便用戶準確描述設計,改善RTL 代碼質量,Primace5.0新增了RTL Template功能,其中包括了常用的Verilog設計元素。Primace5.0還第一次完整支持了8051MCU的SoC仿真以及時序仿真(Timing Simulation)。相對上一代版本,新一代Primace顯著改進了用戶信息提示以及流程的穩定性。本文將簡要介紹這些改進以及對用戶使用體驗的影響,并推薦幾種可以有效改進設計流程,加速設計過程的方法。

Primace5.0主要新增/改善的功能

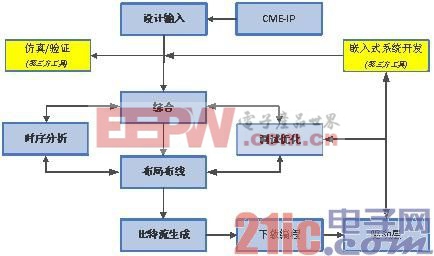

Primace5.0中基本設計流程保持了一貫的簡潔的特點,如圖1所示,主要包括設計輸入(RTL編輯等),設計實現(綜合、布局布線等),時序收斂(以靜態時序分析為基礎的設計、實現調整),以及碼流下載和片上調試(DebugWare等)。

圖1: Primace中FPGA/CAP開發流程

基于時序驅動的布局布線

時序驅動的布局布線是一種已經被廣泛證明與接受的設計方法,設計人員通過描述設計的時序約束(包括核心頻率約束,I/O約束,例外約束,特定路徑約束,跨時鐘域約束等)可以有效指導布局布線程序高效、高質量的完成設計實現。Primace5.0中接受的時序約束包括:

Basic Timing Path

Clock Setup/Hold, Falling edge

Tsu/Th, Tco, Tpd

Advanced Timing Path

False path

Generated clock

User edited sdc

時序約束輸入輔助

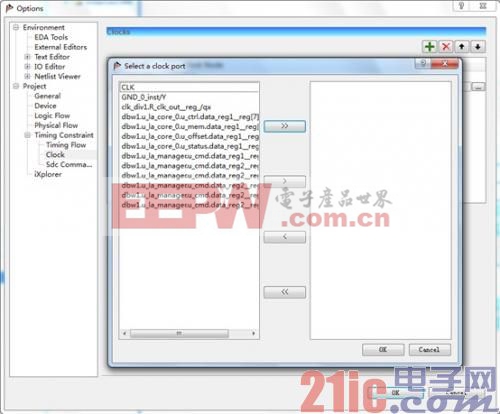

為了方便用戶可以準確高效的輸入時序約束,Primace5.0還配套改進了兼容Synopsys SDC的設計約束輸入界面。如下圖所示:

圖2: 選擇時鐘界面

圖3:時鐘約束設置界面

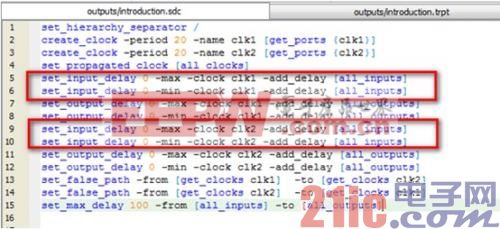

各類SDC最終匯總在統一的SDC約束文件里,用戶可以集中編輯:

圖4:SDC編輯界面

評論