基于FPGA的實(shí)時(shí)視頻圖像采集與顯示系統(tǒng)的設(shè)計(jì)與實(shí)

摘要:主要針對(duì)目前視頻圖像處理發(fā)展的現(xiàn)狀,結(jié)合FPGA技術(shù),設(shè)計(jì)了一個(gè)基于FPGA的實(shí)時(shí)視頻圖像采集與顯示系統(tǒng)。系統(tǒng)采用FPGA作為主控芯片,搭栽專用的編碼解碼芯片進(jìn)行圖像的采集與顯示,主要包括解碼芯片的初始化、編碼芯片的初始化、FPGA圖像采集、PLL設(shè)置等幾個(gè)功能模塊。采用FPGA的標(biāo)準(zhǔn)設(shè)計(jì)流程及一些常用技巧來對(duì)整個(gè)系統(tǒng)進(jìn)行編程。重點(diǎn)在于利用FPFA開發(fā)平臺(tái)對(duì)普通相機(jī)輸出的圖像進(jìn)行采集與顯示,最終能在連接的RCA端口顯示屏顯示。

關(guān)鍵詞:FPGA;視頻圖像采集;編碼芯片;解碼芯片

0 引言

隨著時(shí)代的發(fā)展,人們?cè)趫D像處理領(lǐng)域取得了相當(dāng)多的成果,研究出了很多算法,例如中值濾波、高通濾波等。在圖像的傳輸過程中,各種噪聲源的干擾和影響常常會(huì)使圖像的質(zhì)量變差。由于用一般的軟件實(shí)現(xiàn)的圖像預(yù)處理算法處理的數(shù)據(jù)量大,實(shí)現(xiàn)起來會(huì)比較慢,如果說對(duì)于一些實(shí)時(shí)性要求比較高的系統(tǒng),那么處理速度往往是要考慮的關(guān)鍵要素,因?yàn)橐坏?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/實(shí)時(shí)">實(shí)時(shí)性達(dá)不到,就不能第一時(shí)間記錄下信息。另外,實(shí)時(shí)圖像處理技術(shù)的日新月異和圖像處理系統(tǒng)的發(fā)展有著千絲萬縷的聯(lián)系。在實(shí)時(shí)圖像處理系統(tǒng)中,關(guān)鍵的技術(shù)是對(duì)實(shí)時(shí)圖像的采集和處理,圖像采集的速度、質(zhì)量直接影響到這個(gè)系統(tǒng)的性能。

1 系統(tǒng)硬件設(shè)計(jì)

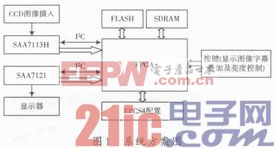

本系統(tǒng)基于FPGA的實(shí)時(shí)圖像與顯示系統(tǒng),由前端視頻采集單元、圖像存儲(chǔ)單元、圖像顯示單元三部分組成。主要功能為對(duì)攝像頭送來的視頻數(shù)據(jù)進(jìn)行采集,并采用專用視頻解碼芯片將模擬視頻轉(zhuǎn)化成數(shù)字視頻;將采集進(jìn)來的數(shù)據(jù)存儲(chǔ)到內(nèi)嵌的SDRAM中;采用專用視頻編碼芯片將數(shù)字視頻信號(hào)轉(zhuǎn)換為模擬信號(hào)送顯示器輸出。系統(tǒng)的方案圖如圖1所示。

系統(tǒng)上電后,F(xiàn)PGA管理單元通過I2C總線對(duì)SAA7113H解碼芯片進(jìn)行初始化;CCD攝像頭輸出的PAL制式模擬視頻輸入SAA7113H解碼模塊。FP GA將解碼后的圖像通過輸入緩沖FIFO存放到外部SRAM;再用SDRAM進(jìn)行奇偶場(chǎng)的合并,滿一幀后圖像進(jìn)入FPGA進(jìn)行內(nèi)部圖像處理,經(jīng)輸出緩沖進(jìn)入SAA7121編碼模塊轉(zhuǎn)換為模擬視頻輸出。通過按鍵的選擇可控制使其輸出圖像亮度增強(qiáng)及字符疊加。本節(jié)將圍繞系統(tǒng)中的視頻圖像解碼芯片及編碼芯片作具體分析。

1. 1 解碼芯片外圍電路

SAA7113H主要由模擬轉(zhuǎn)換電路、亮度信號(hào)電路、色度信號(hào)電路、同步電路、輸出信號(hào)格式、總線控制及時(shí)鐘生成等組成。AI11、AI12、AI21、AI22為四路模擬輸入通道,AOUT為模擬測(cè)試輸出通道,VP00~VP07為解碼輸出通道,這些通道的選擇及格式配置都通過I2C總線來完成的。另外,SDA為I2C總線的數(shù)據(jù)輸入/輸出端,SCL為串行時(shí)鐘輸入端,LLC為行鎖定系統(tǒng)時(shí)鐘頻率輸出信號(hào),頻率為27 MHz,XTALI、XIAL是外部晶振連接端,TDO/TDI為邊界掃描測(cè)試數(shù)據(jù)的輸出/輸入端,TCK、TMS為邊界掃描的時(shí)鐘和測(cè)試模式輸入端。SAA7113H的芯片結(jié)構(gòu)圖如圖2所示。

1.2 編碼芯片外圍電路

SAA7121視頻編碼芯片,可以將數(shù)字的YUV數(shù)字編碼為PAL或者NTSC制式的CVBS輸出或者S端子輸出的模擬視頻信號(hào),單一的3.3 V供電,可通過I2C接口對(duì)芯片內(nèi)部電路進(jìn)行控制。該芯片內(nèi)有三個(gè)片內(nèi)10位視頻D/A轉(zhuǎn)換器分別對(duì)應(yīng)Y,C和CVBS,兩倍過采樣。通過I2C總線協(xié)議對(duì)SAA7121的各個(gè)控制寄存器進(jìn)行配置就可使其滿足系統(tǒng)要求,芯片的最大特點(diǎn)也是在于僅需一個(gè)24. 576 MHz的晶振就可以滿足所有視頻標(biāo)準(zhǔn)的應(yīng)用。

fpga相關(guān)文章:fpga是什么

晶振相關(guān)文章:晶振原理 數(shù)字濾波器相關(guān)文章:數(shù)字濾波器原理

評(píng)論