基于X24C45芯片的非易失性數據存儲設計

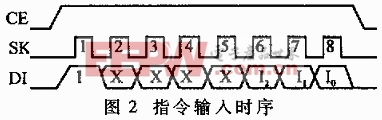

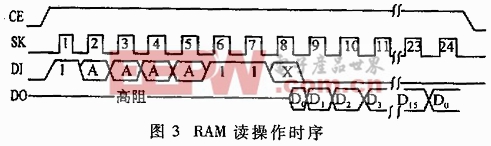

為了少占用CPU的I/O端口,X24C45的DI腳和DO腳通常連接到CPU的同一個I/O口(如圖1所示)。READ指令將RAM中AAAA地址的數據讀出,該指令的最低位為無關位,這樣正好允許在READ指令的第八個時鐘周期內將I/O口由輸出轉換為輸入。RAM的讀操作時序如圖3所示。

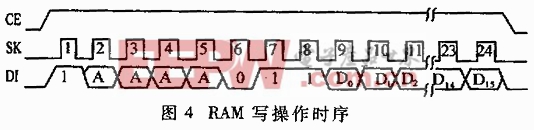

WRITE指令將數據寫入RAM的AAAA地址中,其時序如圖4所示。需要說明的是,RAM中的每個地址存儲16bit數據。

3 X24C45應用時需注意的問題

X24C45實際應用時與CPU的連接如圖1所示。前面已經提到為節省CPU的I/O端口,可以將DI腳和DO腳連接到CPU的同一個I/O口(PA4)。

在此要特別強調的是,電容C和二極管D本來是沒有加上去的,X24C45芯片手冊中也沒有這樣說明。但在實際應用中筆者發現,在沒有加上電容C和二極管D的情況下,X24C45會出現掉電時備份數據出錯的現象。究其原因,是因為在X24C45中將當前數據由RAM存儲到EEPROM時需要一定的時間(該時間典型數值為2ms,最長可達5ms),而且啟動自動存儲的閾值電壓在4.0V~4.3V之間,數據由RAM存儲到EEPROM所需要的最低電源電壓為3.5V,掉電后電源電壓由閥值電壓電路和負載的不同而不同。顯然,掉電后電源電壓由閥值電壓下降到3.5V所需的時間如果少于數據由RAM存儲到EEPROM所需的時間,就會出現一部分數據因不能被及時備份而丟失的問題,而這種問題的出現如果不采取相應的措施是可能被避免的。圖1中的電容C和二極管D可以保證掉電后X24C45電源端的電壓由閥值電壓下降到3.5V所需時間足夠長,從而杜絕掉電時備份數據出錯的情況。

4 X24C45相關操作的軟件實現

X24C45與MC68HC05C4單片機的硬件連接如圖1所示。下面給出與其對應的有關X24C45的前次數據恢復到RAM和自動存儲功能能使設置等操作的軟件編程。

SAMP:LDA #$1C $1C=00011100

STA $04 設置PA2、PA3、PA4為輸出

LDA #$00

STA $00 初始化PA2、PA3、PA4為0

LDA #$85 $85=10000101為RCL指令

STA $81 將RCL指令送至待發送地址

JSR CEHI 調用置CE為高子程序

JSR OUTB 調用輸出8bit子程序

JSR CELO 調用置CE為低子程序

LDA #$82 $82=10000010為ENAS指令

STA $81 將ENAS指令送至待發送地址

JSR CEHI 調用置CE為高子程序

JSR OUTB 調用輸出8bit子程序

JSR CELO 調用置CE為低子程序

……

CEHI:BSET 2,$00 置CE(PA2)為高

RTS

OUTB:LDA #$08 準備移出8個bit

STA $84 將8送至計數器

BCC IS0 C=0轉移至IS0

BSET 4,$00 送1至DI/O(PA4)

BRA IS1 跳轉至IS1

IS0:BCLR 4,$00 送0至DI/O(PA4)

IS1:JSR CLOCK 調用時鐘信號子程序

DEC $84 計數器減1

BNE LOOP 計數器內容≠0跳轉

RTS 計數器內容=0結束

CELO:BCLR 4,$00 將DI/O(PA4)拉低

BCLR 2,$00 置CE(PA2)為低

RTS

CLOCK:BSET 3,$00 置SK(PA3)為高

BCLR 3,$00 置SK(PA3)為低

RTS

限于篇幅,CPU對X24C45其它操作的軟件編程不再贅述。按照上述硬件、軟件的設計思想,已將X24C45成功地應用在電話計費器的設計中。

評論