ASIC后端設計中的時鐘樹綜合

(3)添加buffer。互連線的延時與連線長度的平方成正比,所以插入buffer可以將長的關鍵路徑分成較小的連線,可以有效地減小互連線的延時。插入的buffer的驅動能力的大小靠經驗估計,插入后做時序分析,然后再做re_sizing,直到滿足延時要求。本文引用地址:http://www.104case.com/article/187514.htm

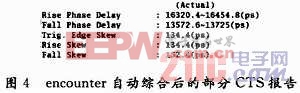

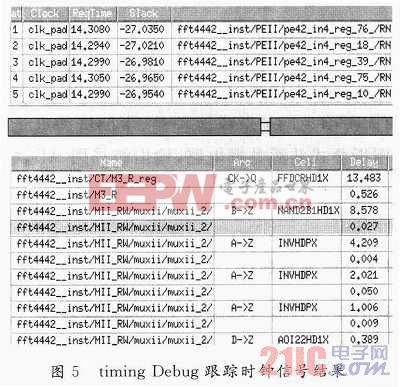

經過eneounter自動時鐘樹綜合后,查看其CTS時序報告,如圖4所示,發現時鐘elk_pad的最大偏移值達到了152.4 ps,這樣與目標值還有很大差距。經過timing Debug跟蹤時鐘信號,如圖5所示,從中找出一些Skew較大的線路,如從fft4442_inst/CT/M3_R_reg/Q到fft4442 _inst/PEII/pc42_in4_reg_76_/RN的延時太長,達到了27.035 ns,因為這樣的線路與其他信號線的延時相差比較大,它們之間的Skew就很容易違規,必須減小它們的延時來減小Skew。

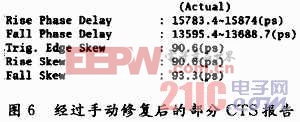

再進一步查看該線路,發現有些單元,如FFDCRHD1X延時達到13.483 ns,HAND281HD1X延時達到8.578ns,INVHDPX也達到了4.209ns,而且該線路還插入了不少BUFHD1X,由于此類buffer的驅動能力太小,從而導致了該線路的延時過大。于是,采用第二類修復辦法:替換(r-e_sizing)驅動能力不一樣的buffer。于是調用Interactive ECO功能,手動將延時太長的單元FFDCRHD1X、HAND2B1HD1X等的尺寸替換為更大的,從而加強其驅動能力,并將部分BUFHD1X替換成BUFHD4X等,再做了PostCTS optimization后,再進行時序分析,這樣經過幾輪反復的修復,降低了一些線路的延時,終于將時鐘CLK的Skew降到了93.3ps,如圖6所示,滿足了設計要求。從eneounter的CTS報告中可以看出,加上有針對性的手動修復之后,對Skew的減小有明顯效果。

3 結語

隨著集成電路設計尺寸的減小和芯片運行頻率的提高,時鐘偏移已經成為影響ASIC芯片性能的關鍵因素。本文以對FFT處理器芯片的時鐘樹綜合為例,分析了時鐘偏移的產生機理及影響,從布局階段就開始關注時序的優化,進行了一系列的優化設置。經過時序分析證明,采取工具自動綜合和手動修復相結合的辦法,容易滿足設計要求,不僅可以提高綜合效率,還可以保證優化的有效性。

評論