開關電源中PWM芯片待機功能的研究

假如,由于負載減小使得主電流峰值降低,且Vcomp降低到一個固定極限(VT1)時,振蕩器頻率將被設置到一個較低的數值上(fsb)。假如,主電流峰值增加且Vcomp超過VT2時,振蕩器頻率將重置在正常值上(fosc)。頻率的變化引起Vcomp的變化,并且由于能量平衡原因而方向相反,因而,提供一個恰當的滯后便可以防止振蕩器頻率在fsb與fosc之間變動。 本文引用地址:http://www.104case.com/article/180733.htm

3 反激式開關電源待機功能的實現

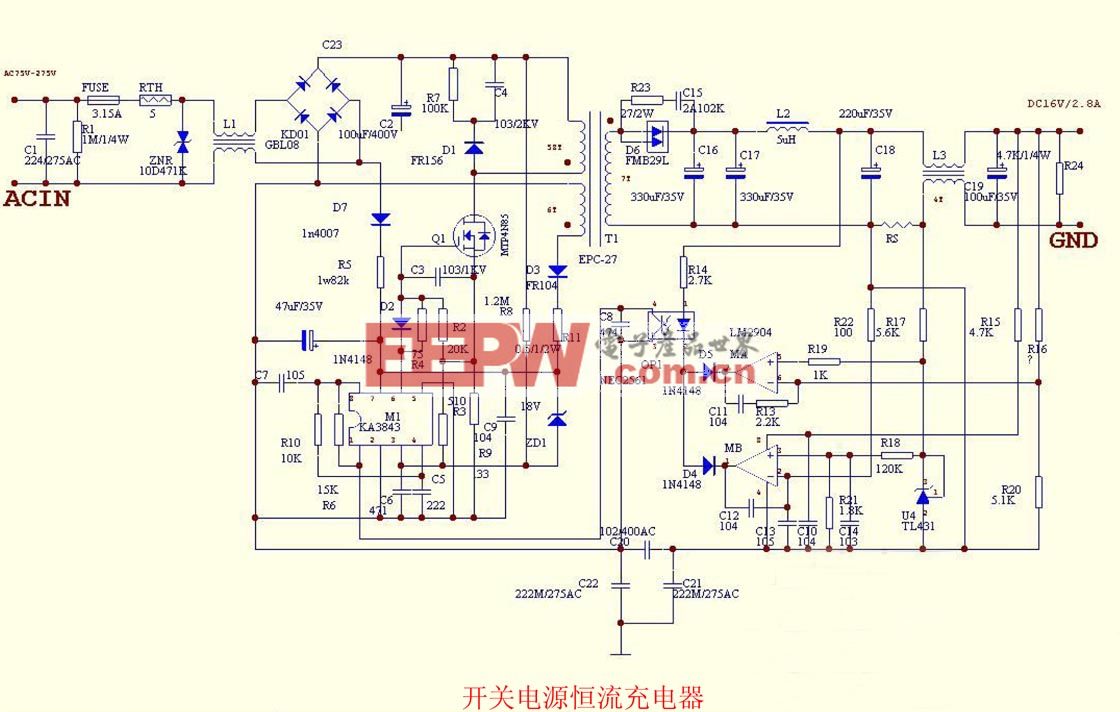

根據上述L5991芯片的待機原理,我們可以試想,在UC3842構成的反激式開關電源的基礎上加入待機功能。通過對與負載相聯系的反饋電壓進行檢測,利用芯片內部的誤差放大器的輸出值,對頻率進行改變。

UC3842芯片的管腳1為誤差放大器輸出,圖2為芯片待機功能的基本電路。

圖2 芯片待機功能的基本電路

該電路的主要原理是:檢測反饋電壓經誤差放大器后的輸出值,通過一個遲滯比較器(施密特觸發器),驅動開關管的開通或者關斷,來實現RT的改變,從而改變電源的振蕩頻率。

我們可以看到,電源處于何種工作狀態(正常工作或是待機),取決于遲滯比較器的閾值的設定,而該閾值取決于電源待機和正常工作時的誤差放大器的輸出值。

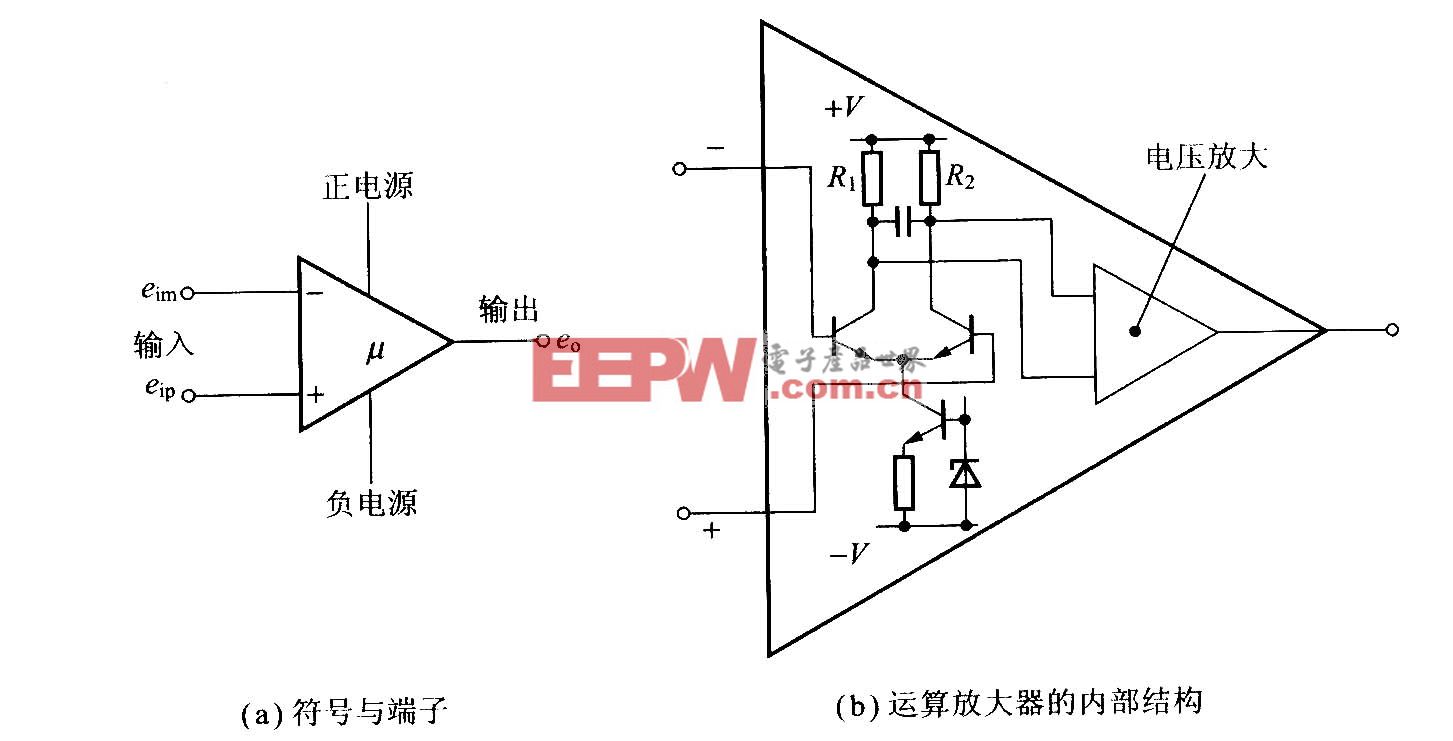

在實際設計的電路中,電源電路空載時,輸出約為1.6V,而非輕載時為1.8V以上,因而,我們根據這個值來設定遲滯比較器的閾值。遲滯比較器由555芯片加上外圍的電阻構成,該比較器的電路圖如圖3所示。

圖3 遲滯比較器電路

圖3中,555芯片的基準電源VDD為+5V,由UC3842的腳8輸出基準電壓給定。遲滯比較器的上下閾值計算如下:

VTH=VDD (3)

VTL= (4)

根據以上確定的閾值,確定各個電阻的阻值。

電源電路負載變化時,根據遲滯比較器的閾值,電源工作在相應的頻率。

4 試驗結果

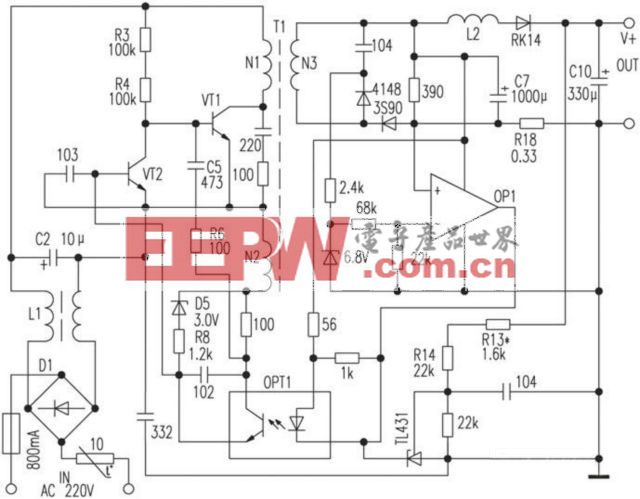

根據以上原理搭構了由UC3842芯片控制的單端反激式開關電源電路[1][2][3],并加入了待機電路,其中取CT=4700μF,RA=RB=20kΩ,驗證了以上原理。

圖4為空載切換成帶5W負載時的頻率變化,頻率由20kHz變成40kHz,而當切換回空載時,頻率則由40kHz變回了20kHz,如圖5所示。

圖4 空載切換成帶負載時頻率變換

圖5 負載切換成空載時的頻率變換

評論