以STM32為核心控制芯片實現閘門測量技術解析方案

在電子工程、資源勘探、儀器儀表等相關應用中,頻率測量是電子測量技術中最基本最常見的測量之一,頻率計也是工程技術人員必不可少的測量工具。但是,傳統的頻率測量方法在實際應用中有較大的局限性,基于傳統測頻原理的頻率計的測量精度將隨被測信號頻率的變化而變化,傳統的直接測頻法其測量精度將隨被測信號頻率的降低而降低,測周法的測量精度將隨被測信號頻率的升高而降低。本文中提出一種基于ARM與CPLD寬頻帶的數字頻率計的設計,以微控器STM32作為核心控制芯片,利用CPLD可編程邏輯器件,實現閘門測量技術的等精度測頻。

本文引用地址:http://www.104case.com/article/171213.htm本設計的技術指標:

測頻范圍:1Hz~200MHz,分辨率為0.1Hz,測頻相對誤差百萬分之一。

周期測量:信號測量范圍與精度要求與測頻功能相同。

占空比測量:準確度99%。

計數范圍:0~1000000000,可手動暫停、復位。

功耗大小:5V×250mA= 1.25W。

等精度測頻原理

常用的直接測頻方法主要有測頻法和測周期法兩種。測頻法就是在確定的閘門時間Tw內,記錄被測信號的變化周期數(或脈沖個數)Nx,則被測信號的頻率為:fx=Nx/Tw。測周期法需要有標準信號的頻率fs,在待測信號的一個周期Tx內,記錄標準頻率的周期數Ns,則被測信號的頻率為:fx=fs/Ns。這兩種方法的計數值會產生±1個字誤差,并且測試精度與計數器中記錄的數值Nx或Ns有關。為了保證測試精度,一般對于低頻信號采用測周期法,對于高頻信號采用測頻法。但由于測試時很不方便,又提出了等精度測頻方法。等精度測頻方法是在直接測頻方法的基礎上發展起來的,它的閘門時間不是固定值,而是被測信號周期的整數倍,即與被測信號同步。 等精度測頻系統的控制時序圖如圖1所示。

圖1 等精度測頻系統的控制時序圖

在測量過程中,有兩個計數器分別對標準信號和被測信號同時計數。首先給出閘門開啟信號(預置閘門上升沿),此時計數器并不開始計數,而是等到被測信號的上升沿到來時,計數器才真正開始計數。然后,預置閘門關閉信號(下降沿)到來時,計數器并不立即停止計數,而是等到被測號的上升沿到來時才結束計數,完成一次測量過程。可以看出,實際閘門時間r與預置閘門時間r1并不嚴格相等,但差值不超過被測信號的一個周期。設在一次實際閘門時間r中,計數器對被測信號的計數值為Nx,對標準信號的計數值為Ns,標準信號的頻率為fs,則被測信號的頻率如式(1)所示。

(1)

圖2為等精度測頻邏輯框圖,CNT1和CNT2是兩個可控計數器,標準頻率信號fs信號從CNT1的時鐘輸入端CLK輸入,經整形后的被測信號fx從CNT2的時鐘輸入端CLK輸入。每個計數器中的CEN輸入端為時鐘使能端,控制時鐘輸入。當預置門信號為高電平(預置時間開始)時,被測信號的上升沿通過D觸發器的輸出端,同時啟動兩個計數器計數;同樣,當預置門信號為低電平(預置時間結束)時,被測信號的上升沿通過D觸發器的輸出端,同時關閉計數器的計數。

圖2 等精度測頻邏輯框圖

系統硬件設計

使用ST公司的32bit處理器STM32F103C8作為主控芯片與高可靠性的可編程邏輯器件EPM240T100C5結合設計成頻率計。

STM32F103C8的功能特點如下:(1) 最高頻率可達72MHz,自帶128/64KB的FLASH,1.25DMIPS/MHz,可以訪問0等待周期的存儲器。(2)供電電壓范圍為2.0~3.6V了,內嵌8MHz高速晶體振蕩器,也可外部時鐘供給,本系統采用CPLD時鐘分頻供給。(3)下載模式可采用串行線調試(SWD)接口和JTAG接口,本系統采用JTAG下載接口。

EPM240T100C5的功能特點如下:(1)支持內部時鐘頻率300MHz,本系統使用有源晶振50MHz供給。(2)片內電壓調整器支持3.3V、2.5V或1.8V電源輸入,本系統使用3.3V電壓供給。(3)下載模式使用10針JTAG接口。

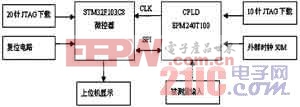

1 系統硬件結構框圖

系統通過對STM32F103C8微控器的控制,經SPI總線向CPLD芯片EPM240T100發送數據和命令來控制內部邏輯單元。EPM240T100使用外部有源晶振50MHz供給,經4分頻12.5MHz作為CPU的輸入時鐘。該系統的硬件結構如圖3所示。其包括主控芯片模塊、JTAG下載模塊、復位電路模塊、上位機顯示模塊、被測量輸入模塊。

圖3 系統框圖

2 系統的數字電路設計

微控器原理如圖4所示。本系統處理器使用STM2F103C8,時鐘由CPLD分頻供給CPU,通過SPI方式將數據和命令傳送給CPLD,而后用串口RS232發送到上位機顯示。

圖4 微控器原理圖

接地電阻相關文章:接地電阻測試方法

評論