基于SoC的MPEG-4視頻解碼加速器

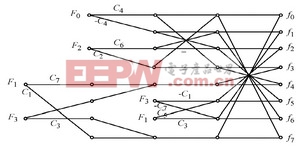

對于Halfzero 的情況, 可簡化圖1 和圖2 中的F(4)、F (5)、F (6)、F (7) 的相關路徑, 得到Halfzero 的算法流程(如圖3)。此時時乘法總數為10 次。

圖3 Halfzero 的算法流程 其中Ci = 2cos( iπ/16)

對于一般的情況, 根據圖1 和圖2 的流程計算,取C i = 2cos( iπ/16) 。乘法總數22 次。

2 硬件結構和設計技巧

2.1 整體結構的選擇

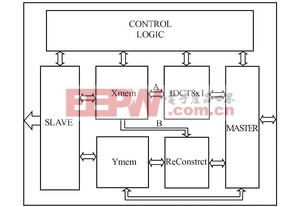

MPEG-4 加速器的的整體框圖如圖4 所示。其中slave 模塊負責模式配置, 接收數據, 反量化并判斷OnlyDC 和Halfzero。寫向slave 的數據經過反量化操作后進入Xmem。MPEG-4 加速器的Cont rol模塊控制整個解碼流程。Idct8x1從Xmem 中讀出原數據做一維IDCT 并寫回Xmem。

由于Xmem 的帶寬限制IDCT 8x1只使用兩個乘法器, 把乘法排列緊湊后, 普通情況一維IDCT 需要20個周期, Halfzero 需要14個周期。Master 負責取運動補償圖像數據, 并在完成IDCT 變換和疊加后將結果放回顯存。每次數據寫回顯存后, Control 模塊會將Xmem 清零, 這樣下次解碼操作只需將非零數據寫入Xmem , 減少了數據的寫入時間。

雙端口片上存儲器Xmem 負責存放IDCT 的中間數據和計算結果, 其中數據通過A端口進行IDCT 變換, IDCT 結果通過B 端口進行疊加, IDCT 計算和運動補償疊加可以通過A、B 兩個端口并行處理。單端口Ymem 負責存放MA STER取回的運動補償數據。Xmem 和Ymem 是零等待的片上存儲器, 而且在外部總線上是可見的, 所以在MPEG-4 加速器不使用時, 它們還可以作為整個芯片高速的緩沖區使用。

圖4 M PEG-4 加速器的整體框圖

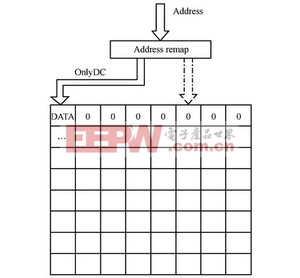

2.2 OnlyDC 情況的處理

在進行二維IDCT 的行變換時, 一般情況和Halfzero情況都會向Xmem 寫回8個計算結果; 如果是OnlyDC 則不對Xm em 做任何讀寫, 所以在做列IDCT時必須對idct8x1 發出的地址進行重新映射, 使其指向這一行的第一個數據。如圖5 所示,IDCT發出的地址指向當前要進行IDCT變換的列中的數據, Control 模塊中的Address Remap 邏輯會根據On lyDC 狀態將地址轉換為指向第一列的有效數據。對于列IDCT 我們直接按照一般情況計算。

圖5 地址重映射

評論