一種基于DDR高速圖像緩存的實現

DDR的存儲單元[2]按照塊(BANK)、行(ROW)、列(Column)地址分布,支持最大猝發操作為8個存儲單元,每次切換塊、行地址必須首先進行充電狀態(Precharge)來關閉當前操作的塊、行中的存儲單元,并且在進行新的操作時首先要激活操作單元所在的塊和行,控制器在工作空閑狀態下發出激活命令(ACTIVE)進入激活狀態,在此狀態下等候應用層發送的控制命令以進行數據操作。

由以上分析可知:由于存在猝發長度限制及塊和行地址切換等控制時間開銷,DDR的隨機操作的數據吞吐量實際上是有限的,不適合高速圖像緩存這種應用環境,必須設計一種新的猝發模式來提高數據吞吐量。本文結合DDR充電以及圖像緩存的特點,提出并實現了一種一次操作DDR一行、一行1 024個存儲單元的猝發模式,由于DDR只支持2、4、8長度的猝發模式,設計中采用了猝發長度為4的連續猝發方式,核心思想是在一次猝發正在進行的時候又發起操作命令從而使得該次猝發后連續進行下一次猝發。實現了一次連續操作2KB數據的高吞吐量操作。如圖2狀態機所示,當一行操作完后則進入空閑狀態,然后再進行自動刷新和充電的操作。這種猝發模式一次猝發只需要一次充電操作,而猝發長度為8的猝發模式完成2KB的數據傳輸共需要進行125次充電操作,而一次充電操作需要幾個時鐘周期開銷,相比較而言,大大節省了控制開銷,提高了數據吞吐量。

1.2 應用層控制模塊

本設計將DDR作為FIFO的容量擴展來實現高速緩存,這需要內部產生地址邏輯。在應用層控制模塊中,負責接收用戶接口模塊送過來的命令信號,并對命令進行譯碼。判斷當前命令與上次命令一樣的時候地址繼續累加產生,當前命令與上次命令不同時則地址復位,重新從DDR的零地址開始操作,這樣符合FIFO的工作特點。模塊產生DDR的地址信號和物理層的控制信號,并根據地址邏輯產生DDR狀態信號反饋到用戶層接口。

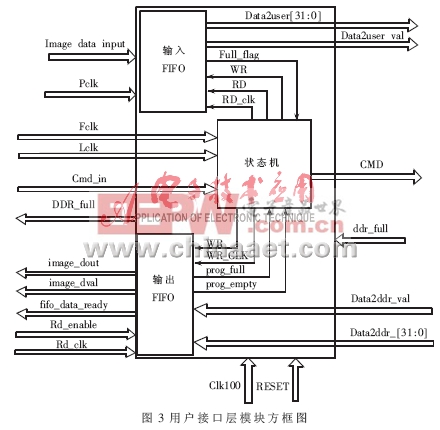

1.3 用戶層接口模塊

用戶層接口模塊[3]負責接收圖像輸入數據,并提供簡易用戶接口,屏蔽了內部控制的復雜性,在用戶看來對該DDR的操作實際上就是對FIFO的操作,判斷DDR內部產生的DDR狀態信號,發出緩存或者數據讀出命令。

用戶接口層模塊方框圖如圖3所示。當用戶發出緩存命令時,內部狀態機自動監測圖像幀的開始位置并將一幀中的幾行數據寫入“輸入FIFO”,當此FIFO達到一次猝發操作數據量2KB時,狀態機發出DDR寫命令到下一層,并一次性讀完輸入FIFO的數據。圖像數據連續向“輸入FIFO”輸入,狀態機不間斷地檢測“輸入FIFO”的編程狀態信號并發出DDR寫命令。由于圖像數據存在行場消隱期以及DDR的行猝發寫操作效率高,因此在一定的像素時鐘條件下不會出現數據堵塞情況。

當用戶發出讀出命令時,狀態機自動檢測“輸入FIFO”的狀態,在可編程空信號有效時一次性向“輸出FIFO”輸入2KB數據,此時“輸出FIFO”輸出數據有效信號以提示用戶可以進行數據讀取。用戶從DDR讀出數據操作實際上就是對FIFO的讀操作,因此用戶只需要提供讀FIFO使能信號以及讀FIFO時鐘就可以將DDR內部的數據依次讀出。當用戶快要將FIFO的數據讀空的時候,狀態機發出讀命令從DDR存儲器中一次性讀出2KB數據存入“輸出FIFO”中,由于DDR讀的峰值速度高達400MB/s(100MHz×2B×2),而用戶接口讀速率一般不超過這個值,因此不會出現數據堵塞情況。

該模塊完成了用戶接口、圖像輸入、控制器三個時鐘域的設計,極大地簡化了用戶接口的操作。良好的功能模塊化劃分,使得用戶只需按照具體要求對圖像輸入接口進行簡單修改便可實現對于任何數據源的緩存,拓寬了該緩存技術的應用范圍。

1.4 時鐘管理單元模塊

本設計DDR控制器時鐘頻率[4]為100MHz,在各模塊中時鐘相位可以不同。因此時鐘管理模塊對時鐘輸入信號進行90°、180°、270°等相移,設計中可以采用FPGA的數字時鐘管理單元(DCM)。該模塊產生復位信號,當上電復位該模塊自動檢測復位信號,并延遲200μs產生控制器所需要的復位信號。

2 性能測試

使用VHDL語言[5]在ISE7.1i軟件環境下完成整個模塊的設計,綜合后共占14%的芯片Slice資源,最高時鐘頻率可達156.5MHz。在基于Xilinx的VirtexIIpro硬件平臺上加載測試,硬件平臺中使用的DDR為Micron公司的MT46V32M16芯片,晶振為100MHz。

為測試該設計的最高平均緩存速度,采用邏輯分析儀采集控制器內部工作時的數據傳輸狀態。發現一行數據的猝發共需要512個時鐘周期,而刷新、充電、狀態等待等時鐘開銷只需要不到50個時鐘周期,因此,實際平均數據吞吐量為理論峰值速率400MB/s×512/(512+50)≈360MB/s。

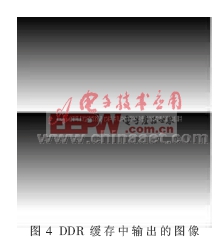

為測試該圖像緩存的數據記錄的完整性,向該模塊輸入模擬產生的相機數據。8位灰度圖像大小為512×512,圖4為從DDR器件中讀出的緩存圖像。

本文設計并實現了一種基于DDR的高速圖像緩存。創新地采用了行猝發操作以提高數據吞吐量。在100MHz的時鐘條件下實現峰值傳輸速率400MB/s、最大平均傳輸速率360MB/s的圖像緩存。在提高時鐘頻率的情況下數據傳輸率還有上升空間。同時用戶可根據需求對輸入接口進行修改以應用于特殊要求的數據緩存,應用廣泛。

評論