手機數字基帶處理芯片中的靜態時序分析

1.引言

本文引用地址:http://www.104case.com/article/167038.htm隨著深亞微米技術的發展,數字電路的規模已經發展到上百萬門甚至上千萬門。工藝也從幾十μm提高到65nm甚至45nm。這樣的電路規模做驗證的時間在整個芯片的開發周期所占的比例會越來越重。通常,在做驗證的時候,我們都會采用動態驗證的方法。現在,用靜態驗證方法(STA Static Timing Analysis),不僅能夠完成驗證的工作,而且還能大大節省驗證所需要的時間。靜態時序分析簡稱它提供了一種針對大規模門級電路進行時序驗證的有效方法。靜態時序分析是相對于動態時序分析而言的。動態時序分析時不可能產生完備的測試向量,覆蓋門級網表中的每一條路徑。因此在動態時序分析中,無法暴露一些路徑上可能存在的時序問題;而靜態時序分析,可以方便地顯示出全部路徑的時序關系,因此逐步成為集成電路設計簽字認可的標準。

2.靜態時序分析工作原理

本文以Synopsys公司的Prime Time SI作為時序分析的工具,介紹靜態時序分析的工作原理。Prime Time把整個設計電路打散成從主要的輸入端口到電路觸發器、從觸發器到觸發器、從觸發器到主要輸出端口、從主要的輸出端口到主要的輸出端口、四種類型的時序路徑,分析不同路徑的時序信息,得到建立時間(setup time)和保持時間(hold time)的計算結果。而Prime time SI又在Prime time的基礎上加入串擾分析(Crosstalk analysis)。串擾是由兩個或者多個物理相鄰連線之間的容性交叉耦合(capacitive cross-coupling)產生的相互作用。隨著工藝越來越進步,在130nm或者90nm的工藝下,串擾的影響已經變得與單元延遲和線延遲一樣重要。

2.1 時序路徑的分析

整個電路的靜態時序分析都是由時序路徑分析組成。時序路徑分析就是檢查從發射沿(lunching edge)到捕獲沿(capturing edge)的時間是否滿足設計的需要。它主要可以分為兩類:

建立時間路徑

這種路徑用于檢查信號在到達捕獲沿之前的一段穩定時間(setup time),也就是確定從發射沿到捕獲沿的過程是否足夠快。建立路徑包括普通的數據到時鐘的建立路徑、數據到數據以及時鐘門的路徑。如果最晚的一個發射沿到最早的一個捕獲沿之間的時間滿足時序要求(沒有timing violation),才能確保這條建立路徑都滿足條件。

保持時間路徑

這種路徑用于檢查信號在到達捕獲沿之后的一段穩定時間的(hold time),也就是確定從發射沿到捕獲沿的時間是否太短。包括普通的數據到時鐘的建立路徑、數據到數據以及時鐘門的路徑、異步信號同步化的檢查。為了正確的分析,我們檢查保持路徑時必須檢查最早的一個發射沿到最晚的一個捕獲沿之間的時間滿足時序要求。

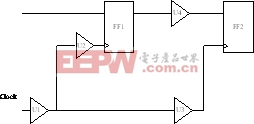

如圖1中發射部分由所有的時鐘端口到觸發器FF2的D端口之間的單元(包括U1、U2、FF1、U4)和線組成;捕獲部分由所有的時鐘端口到觸發器FF2的時鐘端口之間的單元(U1、U3、FF2)和線組成。其中U1既屬于建立路徑又屬于保持路徑。那么,建立路徑就應該結合到FF2的D端口最慢的路徑和到其時鐘端口最快的路徑來看。保持路徑則相反,我們應該找到達FF2D端口最快的路徑和到其時鐘端口最慢的路徑。對于Setup Time驗證來說:

Slack=Required Time C Arrival Time

對于Hold Time驗證來說:

Slack= Arrival Time CRequired Time

Slack為正值,表示滿足時序要求

圖1 建立/保持路徑示意圖

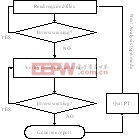

PT工作流程

圖2為PT的工作流程,我們可以看出靜態時序分析是一個反復進行的過程。直到結果滿足要求為止。

圖2 PT工作流程

芯片在工作時所處的環境是不同的,然而環境的不同導致芯片內部的單元和線的延遲不同。為了使芯片在大多數環境下都能正常工作,PT中提供了三種分析模式:single、bc_wc、on_chip_variation。我們平時常用的是bc_wc模式,它把環境用工藝制程(process)、溫度(temperature)、電壓(voltage)分為以下3種情況:

1、best case:工藝制程:1;理想溫度零下40攝氏度;電壓1.32V(此芯片額定電壓為1.2V)

2、typical case:工藝制程:1;室溫環境25攝氏度;電壓1.2V

3、worst case: 工藝制程:1;125攝氏度;電壓1.08V

為了測試芯片在投片生產和封裝整個制造過程是否出現物理等方面的缺陷導致功能不正確。現在的超大規模集成電路的設計中,都加入了可測性設計(DFT:Design for Test)電路。當芯片工作于測試模式時,時鐘樹的結構與功能模式完全不同。我們必須在測試模式下也要分以上3種情況做靜態時序分析。

3.靜態時序分析與門級仿真的關系

靜態時序分析也有自己的弱點,它無法驗證電路功能的正確性。值得注意的是,靜態時序分析只能有效地驗證同步時序的正確性,大部分設計中可能包含地異步電路的時序驗證,則必須通過門級仿真來保證其時序的正確性。

評論