AM-OLED顯示驅動芯片中內置SRAM的設計

2 SRAM電路的低功耗設計

嵌入式SRAM的功耗大致分為動態功耗和靜態功耗。對應到SRAM的具體模塊上,其功耗主要消耗在譯碼器、字線驅動、位線預充、靈敏放大器以及靜態漏電流上。譯碼器可以用與非門邏輯來代替偽NMOS邏輯設計以降低功耗,由于本電路結構沒有靈敏放大器電路,因而無需考慮其功耗。下面主要就動態功耗進行優化。

SRAM電路的動態功耗計算公式如下:

式中,iactive為工作單元的等效電流;ileak為不工作單元的漏電流;CDE為每個譯碼器的輸出節點電容;VINT為內部電源電壓;iDC為讀操作消耗的直流電流;△t為直流電流的激活時間;CPT為CMOS邏輯電路和外圍電路的總電容;IDCP為外圍電路的靜態電流。本文分別從降低位線寄生電容及其電壓擺幅來降低SRAM的整體功耗。

2.1 降低寄生電容

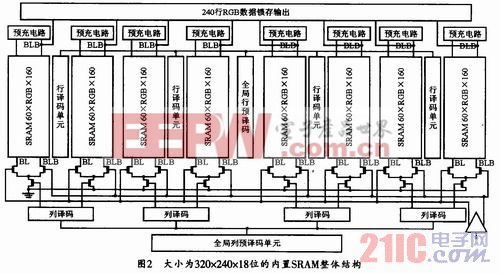

降低寄生電容可采用位線劃分技術(DBL)和字線劃分技術(DWL),即將位線和字線劃分成多級,以降低位線寄生電容和字線寄生電容,這樣即可降低讀寫功耗,也能提高數據的讀寫速度,進一步提高SRAM的整體性能。圖2所示是一個大小為320x240x18位的SRAM存儲陣列的整體結構。該結構將240x18列分成4塊,每塊包含60x18位數據;320行則分成左右兩級,每級含160行。這樣就把整個陣列分成了8個小模塊,每塊大小為160x60x18位,這樣就使得字線電容降到了原來的1/4。位線電容則降為原來的1/2。本文引用地址:http://www.104case.com/article/166194.htm

2.2 降低位線電壓擺幅

由于傳統結構中,整個讀寫過程的預充電路都會對兩條位線進行預充電,故會造成功耗的浪費。而讀電路是采用單邊輸出,位線上的電壓擺幅則必須采用全擺幅形式,因此,只能通過降低寫操作時的電壓擺幅來降低功耗。

評論