基于IDT75K62100 芯片的硬件控制庫設計

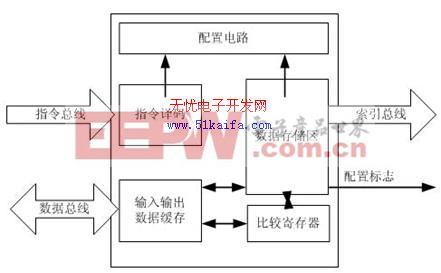

圖 2 :IDT75K62100 內部邏輯結構與外部總線示意圖

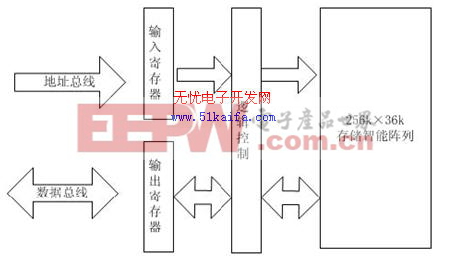

SRAM 選用IDT 公司的71V65603 ,該款SRAM 工作頻率為100M-150MHZ ,支持ZBT 技術,容量為256KX36bit 。其內部邏輯結構及主要外部總線如圖三所示。

圖 3 :IDT71V65603 內部邏輯結構與外部總線示意圖

查找時,先從包頭中提取出查表關鍵字送CAM 查SP,若查到了SP,則將此SP 對應的SA 的地址通過CAM 索引總線送給SRAM 并將匹配標志送IPSec 處理單元,SRAM 根據送來的地址將對應的SA 通過數據總線寫入IPSec 處理單元。每查到一條SA,則需要對SAD 中的該SA 條目進行更新,因為SA 中包括序列號和SA 生存期等需要及時更新的字段。更新過程和查找過程基本一致,先從CAM 中找到對應的SP 條目,得到該SA 的存放地址,然后將修改后的SA 寫入該地址或將原SA 刪除。

一個好的IPSec 協議實現方案,一定程度上取決于SPD 和SAD 條目的合理的設置,因為合理的SPD 和SAD 條目設置可以使IPSec 處理即不復雜,又達到了預期的安全保護的要求。

根據實際需要,本安全模塊的SPD 中每個條目設置源IP 地址,目的IP 地址,傳輸層協議三個選項。需要注意的是,源IP 地址和目的IP 地址項完全沒必要設為128 位的, 只需要儲存各自地址的高64 位即可,因為在128 位的IPV6 地址中,高64 位是所屬網絡地址,由于是在路由器上實現IPSec 保護,故在進行策略查找時,只需要檢查數據包中的源和目的的網絡地址是否與策略庫中的網絡地址相匹配即可。傳輸層協議選項為8 位寬,對于輸出處理單元,只對TCP 和UDP 進行安全保護,故該選項的十進制值應為6(TCP)或17(UDP)

; 對于輸入處理單元,只對ESP 進行處理,故該選項的十進制值應為50。由此看來,SPD 的表項寬度應在136 位以上。

對于輸出包處理的SAD,每個SA 條目包括SPI 字段,序列號計數器字段,序列號溢出字段,密鑰字段和SA 生存期字段。其中,SPI 字段為32 位寬, 取值范圍為256―232-1,我們規定,若SPI 為全1,則表示SA 尚未建立,需要進行協商;若SPI 為其它有效值,則根據對應的SA 進行安全處理。序列號計數器字段為32 位寬,為所處理的數據包提供一個唯一的編號用來抗重放。序列號溢出字段為1 位寬,當該位為‘1’時,表示需要對序列號字段進行溢出檢查;為‘0’表示不需進行溢出檢查。密鑰字段128 位,存放3DES 算法的密鑰。SA 生存期字段16 位寬, 值為預先約定的該SA 所處理的數據包的個數,每處理一包該值減一,為0 時該SA 過期, 重新協商。綜上所述,輸出包處理的SAD1 每個表項寬度應在209 位。

評論