一種基于稀疏矩陣的多核并行擾碼方法

摘要:針對多核環境中高速無線信號的加擾、解擾,提出了一種基于稀疏矩陣的多核并行擾碼方法。首先對輸入信號進行串/并轉換,并將各路信號分別送入對應的處理器核;考慮基于稀疏矩陣的并行擾碼生成器,在單個處理器核內,將其生成的偽隨機碼與輸入信號進行模二加運算,得到單路信號的擾碼輸出;最后將多路并行的擾碼輸出變換為串行輸出。運算量分析結果表明,采用IEEE 802.11n中的擾碼生成多項式,與普通矩陣乘法實現的多核并行擾碼方法相比,基于稀疏矩陣的多核并行擾碼方法,其運算量降低了一個數量級。

關鍵詞:稀疏矩陣;多核;并行擾碼;運算量

0 引言

無線通信速率的不斷提高,要求無線通信設備的處理速度不斷提高。未來無線通信設備處理速度的提高不僅依賴于單處理器處理速度的提高,更主要是依賴于片上處理器核數量的增加。因而,多核處理器被廣泛應用在無線通信信號處理中。

加擾、解擾是無線通信信號處理中的重要環節。隨著無線通信速率的提高,串行擾碼對硬件處理速度的要求越來越高。針對高速信號的加擾、解擾,串行擾碼不再適用。因此,文獻提出了矩陣法實現的并行擾碼方法,首先將串行的高速信號轉換為并行的低速信號,再利用擾碼生成器產生的多個并行相位,同時對輸入并行信號進行擾碼處理。其中,擾碼生成器是基于線性反饋移位寄存器的狀態轉移矩陣實現的。文獻提出了用查表法實現的并行擾碼方法,并行擾碼的步驟與文獻一致,但其擾碼生成器是基于偽隨機序列存儲表實現的。與用矩陣法實現的并行擾碼方法相比,該方法的運算量小,存儲量大。文獻改進了并行擾碼方法的FPGA結構,在該結構中,各路并行擾碼輸出的路徑時延均僅由一個D觸發器和一個異或門構成,該結構對高速信號處理具有很強的適應性。在文獻的基礎上,文獻進一步改進了并行擾碼的FPGA結構,

與文獻的結構相比,在保證輸出路徑時延不變的條件下,該結構減少了寄存器的使用數量。

針對多核環境中的高速無線信號,本文提出一種基于稀疏矩陣的多核并行擾碼方法。該方法應用稀疏矩陣的存儲及運算,產生了并行輸出的偽隨機碼,并實現了多核的并行加擾、解擾。

1 系統模型

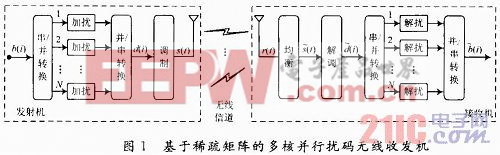

基于稀疏矩陣的多核并行擾碼無線收發機通信鏈路如圖1所示。發射機對比特流b(i)進行基于稀疏矩陣的多核并行加擾,具體步驟為:首先對輸入信號進行串/并轉換,將N路信號分別送入對應序號的處理器核,在單個處理器核內,對輸入信號進行加擾處理;然后將N路并行擾碼輸出經過并/串轉換得到d(i)。d(i)經過調制,產生發射信號s(t)。發射信號經過無線信道到達接收機。接收機對接收信號r(t)進行信道均衡,得到發射信號s(t)的估計值![]() ;然后解調得到比特流d(i)的估計值

;然后解調得到比特流d(i)的估計值![]() ;最后經過基于稀疏矩陣的多核并行解擾恢復出比特流b(i)的估計值

;最后經過基于稀疏矩陣的多核并行解擾恢復出比特流b(i)的估計值![]() 。多核的并行解擾步驟與加擾步驟類似,這里不再贅述。

。多核的并行解擾步驟與加擾步驟類似,這里不再贅述。

評論