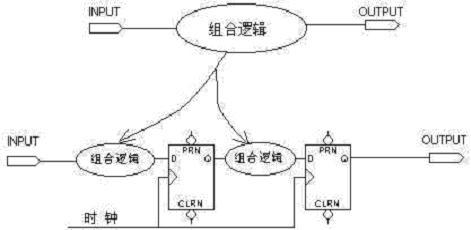

實現(xiàn)拆分大組合邏輯的方法

圖1

可以通過流水線的方式分拆組合邏輯,這也是一種提高芯片速度的一種方式。 在組合邏輯中間插入寄存器,設(shè)計成流水。 很典型的例子就是調(diào)度器,如果做64調(diào)度器,可能中間的延時太長,不能滿足系統(tǒng)速度要求,這時候就可以做成一級16調(diào)度,一級4調(diào)度,來完成64調(diào)度的功能。

用加法器做例子,設(shè)輸入ABCD輸出OUT 上半部分就是: out = A+B+C+D;

下半部分就是:

always @(posedge clk)

begin

sumreg1 = sum1;

sumreg2 = sum2;

sumreg3 = sum3; end

assign sum1 = A+B;

assign sum2 = C+D;

assign sum3 = sumrge1+sumreg2;

assign OUT = sumreg3;

通常建議使用下半部分的算法,如果可以使用流水線。

通常是這樣的,沒有例子看起來是不好理解,但是一有具體的例子就非常清楚了。我也來學(xué)著給個計數(shù)器的例子計數(shù)255,如果用一個寄存器來計那么需要開的深度為8的,如果拆分為兩個那么只需容量為4的兩個寄存器,所需的邏輯較小,不知道對不對。

reg[3:0]ad1;

reg[3:0]ad2;

always @(posedge clk)

if(!rest)

begin

out=0;

ad1=0;

ad2=0;

end

else

if(ad1==15)

begin

ad2=ad2+1;

ad1=0;

end

else

if (ad2==15)

begin out=1;

end

else

ad1=ad1+1;

ad1加滿后去觸發(fā)ad2加。

always @(posedge clk)

if (reset)

counter0 = 0;

else

counter0 = counter0 + 1;

always @(posedge clk)

begin

counterreg0 = counter0;

if (counterreg0 == 4'b1111)

outreg0 = 1;

else

outreg0 = 0;

end

assign counter1 = counterreg1 + outreg0;

always @(posedge clk)

begin

counterreg1 = counter1;

if (counterreg1 == 4'b1111)

out = 1;

else

out = 0;

end

lflhust 寫的程序沒有達到邏輯拆分的目的, 原因很簡單, 那個程序綜合后生成的電路的流水線深度還是1。 zf0579那個程序的流水線深度才是2,達到了拆分的目的。 作邏輯的出發(fā)點不是寫HDL代碼,而是在寫代碼前腦子里面要有 你需要實現(xiàn)的邏輯的電路結(jié)構(gòu)。

作邏輯的出發(fā)點不是寫HDL代碼,而是在寫代碼前腦子里面要有。你需要實現(xiàn)的邏輯的電路結(jié)構(gòu)。

評論