基于ARM嵌入式平臺的X86譯碼SOC架構設計

3 片上總線結構

在ARM SoC體系結構中,有Master和Slave這兩個重要的概念。Master是ARM SoC體系結構中的主單元,他可以向總線發出請求并且對傳輸進行初始化,例如對存儲器進行讀/寫操作,典型的Master可以是CPU,DSP,DMA。Slave是ARM SoC體系結構中的從單元,典型的Slave為片上或者片外存儲器,它們都有自己惟一的地址范圍。Master發起讀/寫操作時,在初始化中會給出讀/寫操作的地址,而地址譯碼器則根據這個地址決定哪個Slave被Master選中,然后相應的Slave做出相應。

在AHB系統中,若有2個Master常需要AccessBus,則系統的Performance必定會下降。為了解決這個問題。ARM提出了Multi-layer AHB,其基本構想是2個Master走不同的Bus去訪問Slave,如果訪問的Slave不同,則兩個Master可以同步的進行Transfer。若彼此訪問一個Slave,則根據優先級去判斷要先處理誰的Transfer。

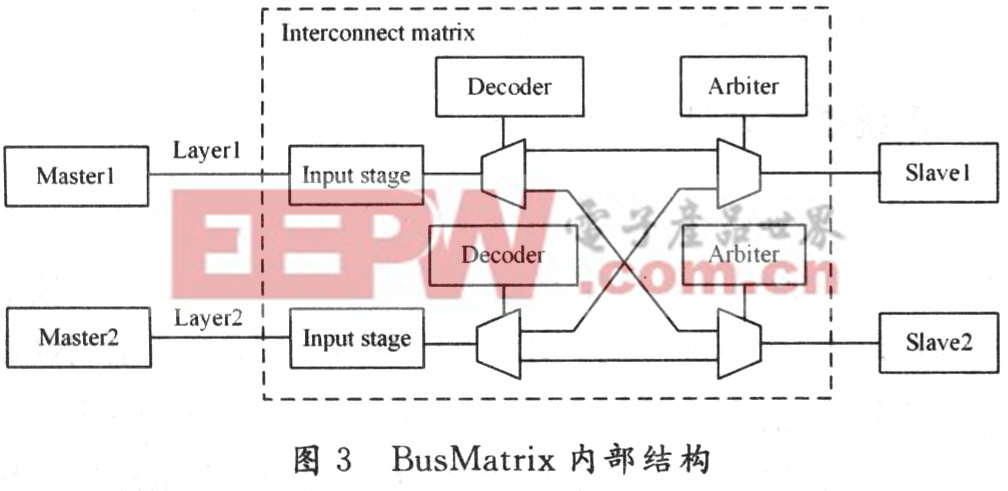

該總線結構使用了Multi_layerbus switch(BusMatrix)模塊。AHB BusMatrix的設計可以分為3個部分:輸入級、譯碼級和輸出級。圖3為該設計所使用的結構,其中,輸入和輸出的個數可以根據系統的Master和Slave靈活調整。 本文引用地址:http://www.104case.com/article/152466.htm

可以看出,每個Layer都有一個譯碼器來決定Master要訪問哪一個Slave,通過多路選擇器實Master和Slave之間的Transfer。。每個Slave口都有自己的仲裁器,該仲裁器使用固定優先級,最高優先級的Layer可以優先訪問對應的Slave。

隨著系統中Master和Slave的增多,Busmatrix模塊的復雜度也會明顯增加,如果按照系統所有的Mas-ter和Slave的個數來確定輸入/輸出口的個數,Busma-trix將會非常復雜,因此對系統結構進行優化變得非常必要。根據系統工作情況可以發現,翻譯模塊的Slave端口僅被ARM7核訪問,即向翻譯模塊存取指令所需的地址,控制其工作,該Slave可以看作是ARM7核私有的,而不被其他Master訪問。有些Slave只有在特殊情況下才被訪問,因此可以將多個Slave看作一個Slave掛在BusMatrix上。優化后的SoC硬件架構如圖4所示。

4 結 語

這里給出了一種具有X86到ARM二進制翻譯和執行功能的SoC系統。利用Multi-layer bus SWitch(BusMatrix)模塊實現Multi-layer。總線結構,在多個核不訪問同一個Slave時,可以同時執行各自功能,有效提高系統的性能,且該總線結構的可擴展性強。同時根據系統工作的特點,對總線結構進行了優化,減小了總線的復雜度。

評論