Chirp函數的Nios Ⅱ嵌入式實現

摘 要:首先分析Chirp函數在頻域上的一般特性,提出利用FPGA的嵌入式軟核NiosⅡ處理器在嵌入式操作系統μC/OS-Ⅱ上實現Chirp的方法,即通過NiosⅡ處理器根據Chirp函數在頻域上頻率的跳變情況實時改變輸出DDS(直接數字合成序列)模塊的頻率步進控制字的辦法,控制DDS模塊的頻率輸出,實現Chirp函數所要達到的掃頻輸出性的目的。通過在NiosⅡIDE編程環境中的Console窗口觀察,該設計能很好地實現Chirp函數功能。

關鍵詞:μC/OS-ⅡSoPC;DDs;FPGA;Chirp函數

0 引 言

SoC(System on(2hip)是20世紀90年代提出的概念,它是將多個功能模塊集成在一塊硅片上,提高芯片的集成度并減少外設芯片的數量和相互之間在PCB上的連接,同時系統性能和功能都有很大的提高。隨著FPGA芯片工藝的不斷發展,設計人員在FPGA中嵌入軟核處理器成為可能,Altera和Xilinx公司相繼推出了SoPC(System on a Programmable Chip)的解決方案,它是指在FPGA內部嵌入包括(;PtJ在內得各種IP組成一個完整系統,在單片FPGA中實現一個完整地系統功能。與SoC相比,SoPC具有更高的靈活性,FPGA的可編程特性使之可以根據需要任意定制SoC系統;與ASIC相比,SoPC具有設計周期短,設計成本低的優勢,同時開發難度也大大降低。由于電磁波在傳輸過程中,經過色散介質如不均勻的波導,高空電離層時會發生色散現象,Chirp函數在射電天文信號的消色散處理中發揮著重要的作用,研究在FPGA中實現Chirp函數是基于FPGA的射電宇宙信號處理的重要組成部分。

l 系統總體設計

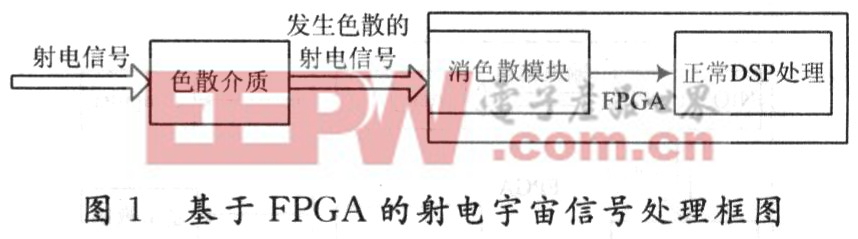

圖1為基于FPGA的射電宇宙信號處理框圖。

該設計是基于SoPC技術設計的Chirp函數信號發生器,該系統把微處理器模塊和DDS模塊集成到單片FPGA芯片內部,通過在嵌入式操作系統μC/OS-Ⅱ編寫的程序,實時控制微處理器對DDS的控制字輸出,DDS模塊根據頻率控制字的不同,輸出不同的數字化正弦波。使之符合Chirp函數的時變頻率特征。Chirp函數根據輸出頻率的遞變規律一般分為兩種:線性Chirp函數和非線性Chirp函數,以下是兩種Chirp函數在頻域上的表現圖如圖2,圖3所示。

從圖2,圖3可以看出Chirp函數的頻率輸出與時間的f-t關系可以總結為:

(1)對于線性Chirp函數

在連續域時間域內有關系式:

![]()

式中:k為常數;f0為初始輸出頻率;t為連續時間。

在離散時間域有關系式:

![]()

式中:k為常數;f0為初始輸出頻率;n為采樣點。

(2)對于非線性Chirp函數

在連續域時間域內有關系式:

![]()

式中:f為非線性函數;f0為初始輸出頻率;t為連續時間。

在離散時間域有關系式:

![]()

式中:f為非線性函數;f0為初始輸出頻率;n為采樣點。

評論