利用FPGA加密芯片的抗DPA攻擊電路設計

0 引言

本文引用地址:http://www.104case.com/article/151255.htm

近年來,現場可編程門陣列(Field Programmable Gate Array,FPGA)由于其高性能、低價格、高開發速度、方便的編程方式等特點得到了廣泛的應用。但對FPGA進行DPA(Differential Power Analysis,差分功耗分析)攻擊已經成為FPGA應用中信息安全的主要威脅之一,受到了廣泛的關注。

DPA是SCA(Side Channel Attacks,旁路攻擊)技術的一種,其攻擊思想為:以電路的功耗特性為基礎,利用功耗與內部密鑰的關系,將大量采樣到的包含該內部密鑰運算的功耗波形數據根據所猜測的密鑰進行劃分,使得所劃分的兩部分具有不同的功耗特性。最后,對兩部分的功耗數據相減得到功耗差分曲線,如果猜測正確,差分曲線將出現明顯的尖峰。

本文將應用FPGA的自身結構特點,結合目前常用的抗DPA攻擊的電路級防護技術,深入研究與分析在FPGA平臺上實現針對DPA攻擊的電路級防護技術。

1 FPGA上的電路防護技術

1.1 FPGA的底層結構

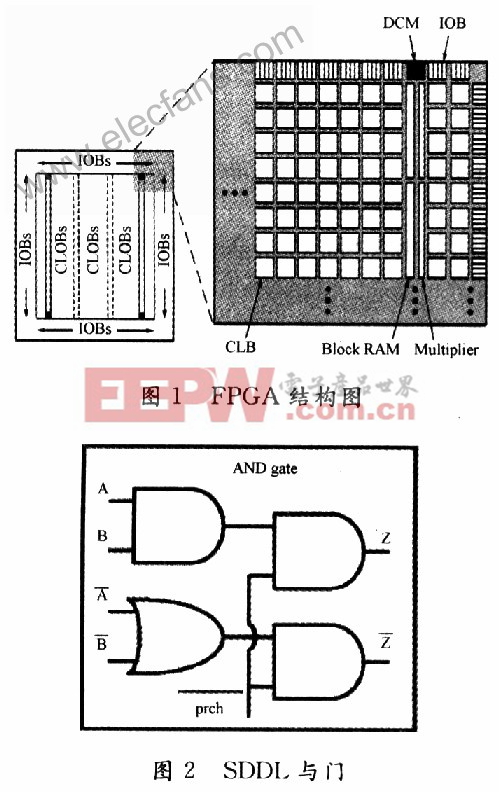

FPGA的簡化結構如圖1所示。FPGA內部最主要的、設計工程中最需關注的部件是CLB(Configurable Logic Block,可配置邏輯塊),IOB(Input/Output Block,輸入/輸出塊),Block RAM(塊RAM)、DCM(Digital Clock Manager,數字時鐘管理器)和Multiplier(乘法器)。其中CLB是FPGA具有可編程能力的主要承擔者,Virtex-5的一個slice的主要組成單元包括4個6輸入查找表、4個觸發器和若干個選擇器。

1.2 雙軌電路技術的實現

雙軌電路技術是指無論是輸入還是輸出都是用兩根線來表示的。由圖2可見,在SDDL與門中,信號A就由A和![]() 共同表示,而輸出Z也由Z和

共同表示,而輸出Z也由Z和![]() 表示。在這種表示下,一個變量可以有4種不同的邏輯值(0,0),(0,1),(1,0)以及(1,1)。SDDL將(0,1)和(1,0)分別用來表示邏輯0和邏輯1。這樣電路內部的邏輯0和邏輯1就變成了對稱的,從而使得各自的功耗相同。另外,邏輯門還引入了一個prch預充電信號。在prch有效的情況下,輸出是(O,0),這個值也就是變量為預充電時在電路中的表示方式。電路的工作分為兩個狀態:運算狀態和預充電狀態。這兩個狀態交替更換,也就是在prch上加載一個固定周期的脈沖。如此一來,電路中變量值的變化就是(0,O)到(O,1)或(1,O),或者是(0,1)或(1,0)到(O,0),每次翻轉都是只有一根信號線進行翻轉。邏輯O和邏輯1達到了完全的平衡。

表示。在這種表示下,一個變量可以有4種不同的邏輯值(0,0),(0,1),(1,0)以及(1,1)。SDDL將(0,1)和(1,0)分別用來表示邏輯0和邏輯1。這樣電路內部的邏輯0和邏輯1就變成了對稱的,從而使得各自的功耗相同。另外,邏輯門還引入了一個prch預充電信號。在prch有效的情況下,輸出是(O,0),這個值也就是變量為預充電時在電路中的表示方式。電路的工作分為兩個狀態:運算狀態和預充電狀態。這兩個狀態交替更換,也就是在prch上加載一個固定周期的脈沖。如此一來,電路中變量值的變化就是(0,O)到(O,1)或(1,O),或者是(0,1)或(1,0)到(O,0),每次翻轉都是只有一根信號線進行翻轉。邏輯O和邏輯1達到了完全的平衡。

評論