數(shù)字下變頻(DDC)中坐標(biāo)變換模塊的ASIC實(shí)現(xiàn)

2.4 硬件實(shí)現(xiàn)結(jié)果

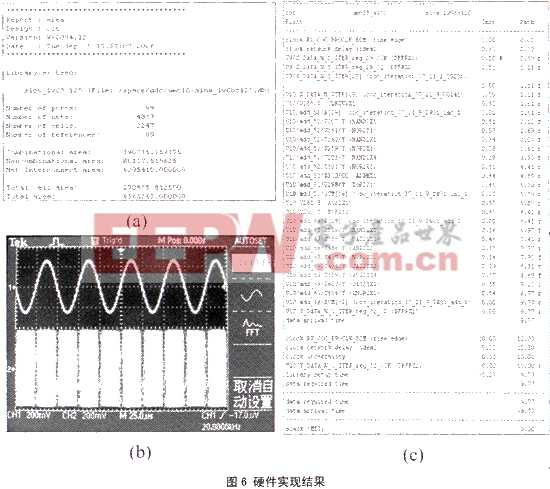

在硬件實(shí)現(xiàn)時(shí),用verilog語(yǔ)言對(duì)坐標(biāo)變換模塊進(jìn)行描述,為滿足DDC的精度要求進(jìn)行了18次迭代,并用DC基于UMC0.18μm的庫(kù)進(jìn)行了綜合,硬件實(shí)現(xiàn)結(jié)果如圖6所示。

圖6(a)是DC綜合后的面積報(bào)告,圖6(c)是關(guān)鍵路徑的時(shí)序報(bào)告,綜合后的最大路徑延時(shí)為9.77ns,完全可以滿足本模塊數(shù)字下變頻器100MHz的處理速度要求,綜合出的單元(cell)的總面積僅為0.27。圖6(b)是該設(shè)計(jì)在FPGA上驗(yàn)證的結(jié)果,該DDC的工作頻率為80MHz,通道2為輸入的基帶信號(hào)頻率20kHz,載波頻率5MHz,頻偏200KHz的FM信號(hào),通道1是通過DDC下變頻后交給坐標(biāo)變化模塊的I,O兩路信號(hào)求出的相位信息,即頻率為20kHz的正弦信號(hào),由圖可知該沒計(jì)實(shí)現(xiàn)了坐標(biāo)變換功能。

3 結(jié)論

使用CORDIC算法,并用流水結(jié)構(gòu)實(shí)現(xiàn)幅度相位的求取可以獲得較高的處理速度,增加迭代次數(shù)可以獲得更高的處理精度,但會(huì)耗費(fèi)較多的資源,在設(shè)計(jì)時(shí)應(yīng)根據(jù)需要,合理的確定迭代次數(shù)。該設(shè)計(jì)已成功應(yīng)用于高速數(shù)字下變頻芯片中。

評(píng)論