微處理器的低功耗芯片設計技術詳解

低功耗設計足一個復雜的綜合性課題。就流程而言,包括功耗建模、評估以及優化等;就設計抽象層次而言,包括自系統級至版圖級的所有抽象層次。同時,功耗優化與系統速度和面積等指標的優化密切相關,需要折中考慮。下面討論常用的低功耗設計技術。

2.1 動態電壓調節

由式(1)可知,動態功耗與工作電壓的平方成正比,功耗將隨著工作電壓的降低以二次方的速度降低,因此降低工作電壓是降低功耗的有力措施。但是,僅僅降低工作電壓會導致傳播延遲加大,執行時間變長。然而,系統負載是隨時間變化的,因此并不需要微處理器所有時刻都保持高性能。動態電壓調節DVS (Dynarnic Voltage Scaling)技術降低功耗的主要思路是根據芯片工作狀態改變功耗管理模式,從而在保證性能的基礎上降低功耗。在不同模式下,工作電壓可以進行調整。為了精確地控制DVS,需要采用電壓調度模塊來實時改變工作電壓,電壓調度模塊通過分析當前和過去狀態下系統工作情況的不同來預測電路的工作負荷。

2.2 門控時鐘和可變頻率時鐘

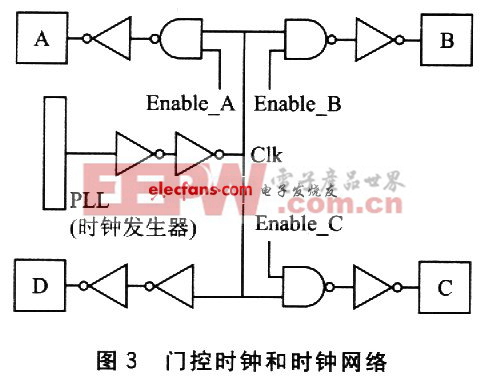

如圖1所示,在微處理器中,很大一部分功耗來自時鐘。時鐘是惟一在所有時間都充放電的信號,而且很多情況下引起不必要的門的翻轉,因此降低時鐘的開關活動性將對降低整個系統的功耗產牛很大的影響。門控時鐘包括門控邏輯模塊時鐘和門控寄存器時鐘。門控邏輯模塊時鐘對時鐘網絡進行劃分,如果在當前的時鐘周期內,系統沒有用到某些邏輯模塊,則暫時切斷這些模塊的時鐘信號,從而明顯地降低開關功耗。圖3為采用“與”門實現的時鐘控制電路。門控寄存器時鐘的原理是當寄存器保持數據時,關閉寄存器時鐘,以降低功耗。然而,門控時鐘易引起毛刺,必須對信號的時序加以嚴格限制,并對其進行仔細的時序驗證。

另一種常用的時鐘技術就是可變頻率時鐘。它根據系統性能要求,配置適當的時鐘頻率以避免不必要的功耗。門控時鐘實際上是可變頻率時鐘的一種極限情況(即只有零和最高頻率兩種值),因此,可變頻率時鐘比門控時鐘技術更加有效,但需要系統內嵌時鐘產生模塊PLL,增加了設計復雜度。去年Intel公司推出的采用先進動態功耗控制技術的Montecito處理器,就利用了變頻時鐘系統。該芯片內嵌一個高精度數字電流表,利用封裝上的微小電壓降計算總電流;通過內嵌的一個32位微處理器來調整主頻,達到64級動態功耗調整的目的,大大降低了功耗。

p2p機相關文章:p2p原理

評論