FPGA實現多處理器解決方案

本文引用地址:http://www.104case.com/article/149403.htm

擴展指令集

多個處理器IP供應商能夠擴展處理器指令集,以包含在硬件中實施的專用算法,并在FPGA中實現。采用處理器常用的加載/存儲操作,數據可饋入到定制邏輯模塊中,成為處理器算法邏輯單元(ALU)的一部分。在有些情況下,定制指令能夠支持多周期操作,實現對FIFO和存儲器緩沖等其他系統資源的訪問。定制指令的典型應用包括位處理、復雜的數值和邏輯運算等。

依靠處理器加載和存儲操作,定制指令與采用通用ALU資源運行同樣算法相比,具有明顯的性能優勢。例如,64kbyte的循環冗余校驗(CRC)以定制指令運行時,運行速度比軟件快出27倍1。不同的應用具有不同的性能結果,但是總體上比單獨采用軟件快得多。

處理器IP供應商不同,開發人員如何使用定制指令也各不相同。例如,在加入定制指令時,有的必須生成一個新的編譯器。然后,根據應用標準,這種定制編譯器導出定制指令調用。更簡單的方法是由用戶在其C源代碼中作為子程序來直接調用指令。由于軟件設計人員能夠更清楚的掌握何時使用定制指令,因此這種方法更自然一些。

提升系統性能的多種方法

其他提升系統整體性能的方法包括利用硬件加速(也稱為協處理器)、處理器協同芯片以及定制片內系統等。

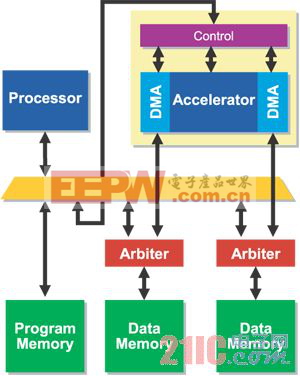

與定制指令不同,硬件加速器作為獨立的邏輯模塊直接從嵌入式CPU獲取指令,不需要CPU干預,處理全部數據緩沖。一個簡單的模塊框圖包括帶有兩個1/2 DMA通道的處理模塊(一個讀取輸入數據,另一個存儲結果)以及一個控制接口,用于CPU建立、啟動、停止以及工作中對各單元的輪詢等。這種體系結構非常適合于對大塊數據的處理,此時,CPU加載數據并存儲結果成為性能瓶頸。

硬件加速器由于其固有的自治特性,能夠比軟件運行任務提高幾個數量級的性能增益,因此加速功能通常在硬件中設計實現。

不管CPU是否在FPGA內部,與FPGA連接的分立處理器和DSP協同芯片都可以使用硬件加速、擴展外設以及接口橋接等。現在,可直接使用芯片間接口IP,實現對FPGA內部外設、加速邏輯和I/O接口的外部訪問。

總結

在FPGA中采用多個軟核處理器,根據時間和功耗要求劃分任務,可高效使用處理能力,與分立處理器相比,具有相同甚至更高的整體性能。多個軟核處理器還可以用作分而治之的策略,來提升系統整體性能或者卸載現有處理器任務,這種策略僅受目標FPGA邏輯和存儲器資源的限制。

一類新的硬件開發工具、知識產權內核以及FPGA體系實現了這些技術的主流應用。在嵌入式領域,由于這些技術的成功,主要FPGA供應商進一步加大了開發和投入。在您下一個設計中,應考慮如何應用這些技術。

評論