FPGA實現多處理器解決方案

尋求高性能處理能力的嵌入式設計人員在成本、性能、功耗上,不可避免的面臨類似“百慕大三角”的困境,無法同時實現三者的最佳組合,而只能達到其中的兩個目標。定制ASIC設計適用于那些能夠負擔得起時間、費用和風險的少數人,但是由于器件尺寸持續減小,而ASIC設計成本不斷攀升,完全定制設計受成本限制,能夠應用的領域越來越少。

本文引用地址:http://www.104case.com/article/149403.htm具有多個軟核處理器的FPGA嵌入式系統為嵌入式設計人員提供了強大的多種功能選項,通過定制功能配置性能最佳的片內系統不再是ASIC設計人員的專利。現在,開發人員能夠趕在產品進入最終測試之前,對其嵌入式系統性能特性進行修改。開發人員還可以延長產品生命周期,將產品迅速推向市場,通過互聯網對硬件和軟件功能進行遠端升級。

盡管術語“多處理器”會使人聯想起學術文章中的“并行處理”一詞,實際商用的單器件多CPU則簡單明了得多。開始進行一個新設計時,開發人員必須考慮一定的性能標準。多個軟核處理器之間的任務劃分具有很大的設計靈活性,實現了由于規范或競爭產品變化而進行的最后一刻設計更改,同時能夠與這些性能標準保持同步。

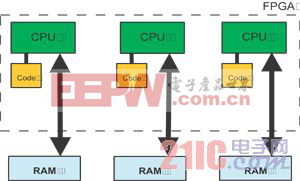

多軟核處理器可作為一種分而治之的策略來提高系統整體性能,或者卸載現有處理器任務。設計人員通常采用400MHz~800MHz的分立處理器實現簡單和復雜的多種器件任務。采用多個軟核處理器,可根據時間和功耗要求,通過任務劃分,更高效的發揮處理能力,提供同樣甚至更好的整體性能。

單個FPGA中能夠實現的軟核處理器數量僅受器件資源的限制(如,邏輯和存儲器資源)。例如,高密度FPGA可以含有幾百個軟核處理器,并且可以采用不同類型的軟核處理器,如16位或32位、性能最佳、邏輯面積最佳處理器等。

根據任務不同,編碼算法由多個處理器進行分擔。專用處理器承擔對時間要求嚴的任務,而要求不高的任務則由一個或多個其他CPU分擔。這種靈活性實現了任務的邏輯分組,能夠以較低的時鐘頻率和功耗實現較高的性能。

FPGA中的嵌入式處理器

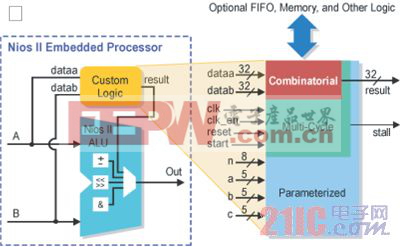

ASIC設計人員對構建定制器件進行了多年的研究,因此,我們不難想象定制器件應包含一組合適的外設、存儲器接口和處理功能。直到1990年后期,FPGA才能夠提供足夠的片內存儲器、可編程邏輯等基本性能資源來實現經濟可行的定制FPGA嵌入式處理器器件。現在,可直接使用專為FPGA設計的嵌入式IP功能(包括CPU、信號處理引擎、外設和標準通信接口等),與傳統分立的嵌入式器件相比,它具有成本和性能的雙重優勢。

從本質上看,設計人員對問題的劃分與在印刷電路板上構建一個多處理器系統相類似。每一部分分配不同的任務,一個處理器進行一般的系統管理(風扇監控、人機接口、系統控制臺等),其他的則處理通信、信號處理、統計收集等系統任務。

多處理器方案將分立的處理器功能由電路板移到FPGA內部,從而降低了器件整體成本,也同時減小了電路板尺寸。這種方案需要較少的互連,減少了處理器之間的信號布線。更多的低級處理器運行在更低的時鐘頻率上,減少了電路板層數。

該方法還可以降低軟件設計成本,減少80%由于耗時的代碼編寫而造成的系統整體設計時間代價。如果任務能夠劃分給多個處理器,那么工程師就能夠直接迅速的進行源代碼編寫、調試和維護。產品成熟時,由于可以方便的對源代碼進行分析,因此代碼維護比較輕松。

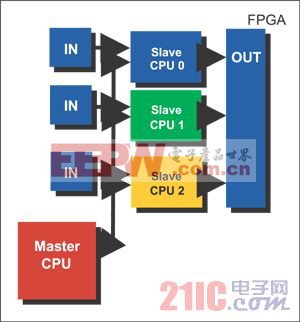

多通道應用

多通道應用采用單芯片多處理器來滿足系統吞吐量要求,每個處理器專用于處理全部通道吞吐量的不同部分,它們運行完全相同的源代碼,也可以根據系統要求靈活的改變算法。在有些情況下,加入主處理器來處理一般的系統管理任務,如系統初始化、統計收集和錯誤處理等。

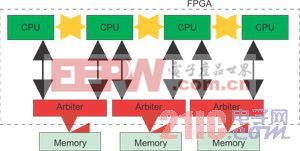

串行鏈接的處理器

系統結構將一個鏈上的幾個處理器組合對待為更復雜流水線上的一級。每個CPU負責全部處理任務的一部分,共享數據存儲器(片外采用仲裁或專用存儲器接口,片內采用雙端口存儲器),將結果由一級的輸出傳向下一級的輸入。

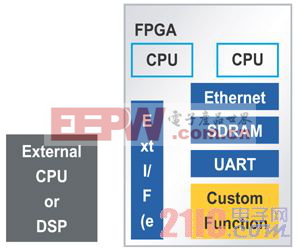

處理器協同芯片

不管CPU是否在FPGA內部,與FPGA連接的分立處理器和DSP芯片也可以使用硬件加速、外設擴展和接口橋接等。現在,可直接使用芯片間接口IP,實現對FPGA內部外設、加速邏輯和I/O接口的外部訪問。

確定處理器性能

在應用軟件還沒有明確時,很難確定嵌入式系統的處理器性能。業界標準會有一些幫助,但是在軟件完成之前,一切都具有不確定性。這使得設計人員非常謹慎,擔心低估性能要求,而選擇高于所需性能(價格也高)要求的器件。如果設計人員能夠準確的預測所需性能,那么選擇處理器將變得非常簡單。這種預測要考慮對時間要求嚴的任務以及一個或多個低級任務所產生的負載對性能的要求。

基于FPGA的嵌入式系統提供靈活的性能,支持最后一刻更改,根據客戶要求來提升系統性能。將

含有大量計算的算法轉換為FPGA中的邏輯后,其運行速度比微處理器或數字信號處理器實現的相同軟件算法快出幾個數量級。更重要的是,硬件資源可提供給對性能要求高的算法,從而降低了對高性能CPU的需求,并降低了時鐘頻率和功耗,簡化了電路板設計。

評論