一種提高系統響應速度的SoC系統架構

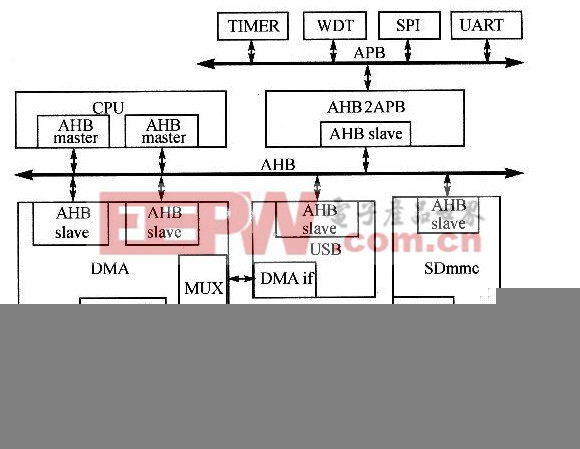

為了解決因圖1所示架構大批量數據傳輸而引入DMA產生的問題,提出了包含2個AHB接口的DMA控制器的SoC系統架構。在AHB總線上的sla-ve接口都是不能發起傳輸的,它的一切操作都是被動的。因此圖2中的DMA控制器的主要功能是提供需要進行DMA傳輸的外設接口與處理器讀寫主存的通道以及它們間優先級設定。在此雙AHB從接口的DMA控制器中處理器優先級永遠最高,其他外設通道都可以相互設置優先級,而且除處理器外,為了防止同一個外設長期占用DMA總線的使用權,可對外設DMA通道設置回退(暫時釋放DMA總線)。如當通道2需要與Memory進行數據傳輸時,先向DMA控制申請總線使相應通道2的REQ信號有效,若DMA控制器允許通道2進行數據傳輸,則向通道2響應ACK應答信號。當通道2傳輸完,DMA控制回退長度的寄存器設定的值進入回退階段,若數據傳輸完成,則使REQ信號無效,否則繼續使REQ信號有效,并在回退期后當DMA總線空閑時參于DMA總線競爭。在總線空閑時只有不處于回退期間的最高優先級的通道才能獲得DMA總線使用權,對Memory進行讀寫。

經過Design Compiler邏輯綜合,DMA控制器在SMIC0.18μm的工藝下,能夠達到AHB時鐘域90MHz。能滿足所設計SoC系統時鐘的要求。

2.4 2種架構性能對比

在圖1所示架構中,每次DMA傳輸都要發起1次讀與1次寫操作。若在DMA傳輸期間有需要緊急處理的異常響應,AHB總線此時又被DMA控制器占用,則處理器只能等DMA控制器釋放AHB總線后才能占用AHB總線進行操作,影響處理器效率與系統對異步事件的響應速度。

圖2中是通過DMA控制器的一個通道與Memory相接。DMA控制器包含2個AHB的slave接口,一個是用來對DMA控制器的內部寄存器進行配置,而另一個是被處理器用來對Memory進行讀寫。首先處理器可以利用Cache中的指令與數據來運行,若出現沒命中的問題,也可以對AHB總線上其他存儲區域進行訪問,因為此時AHB總線沒有因DMA傳輸而被占據。并且除處理器通道外,對于其他所有通道的DMA傳輸都可以設置回退,

從而使處理器在外設DMA傳輸期間盡快獲得DMA總線,對掛接在DMA控制器上的Memory能盡快進行讀寫,從而提高處理器的效率。當異常中斷發生時,處理器也能盡快對響應中斷,提高系統對異步事件的響應速度,從而提高系統的實時性。這樣的架構在一定程度上解決了上述架構所產生的影響處理器效率的問題。

3 總結

通過對2種不同架構的分析得出,包含雙從AHB接口DMA技術的SoC系統架構,不僅解決了外設與Memory間的大批量數據傳輸問題,同時又解決了因DMA技術的引入而帶來的處理器對異步事件響應速度過慢及處理器效率變低的問題,提高了對異常中斷的響應速度,使系統更健壯。

評論