應材:半導體材料改善對芯片性能提升至關重要

半導體設備大廠應材(Applied Materials)的磊晶設備部門主管Schubert Chu表示,半導體材料的改善在每個制程節點對 IC性能提升的貢獻度達近90%,該數字在2000年時僅15%。

本文引用地址:http://www.104case.com/article/147518.htmChu在近日于美國舉行的Semicon West 展會上接受訪問時表示,在智慧型手機與平板裝置成為電子產業鏈需求主力的「行動時代」,半導體元件設計的焦點集中于在提升電晶體性能的同時,也需要降低元件的功耗;而在過去的「PC時代」,功耗通常都不是最大的考量。

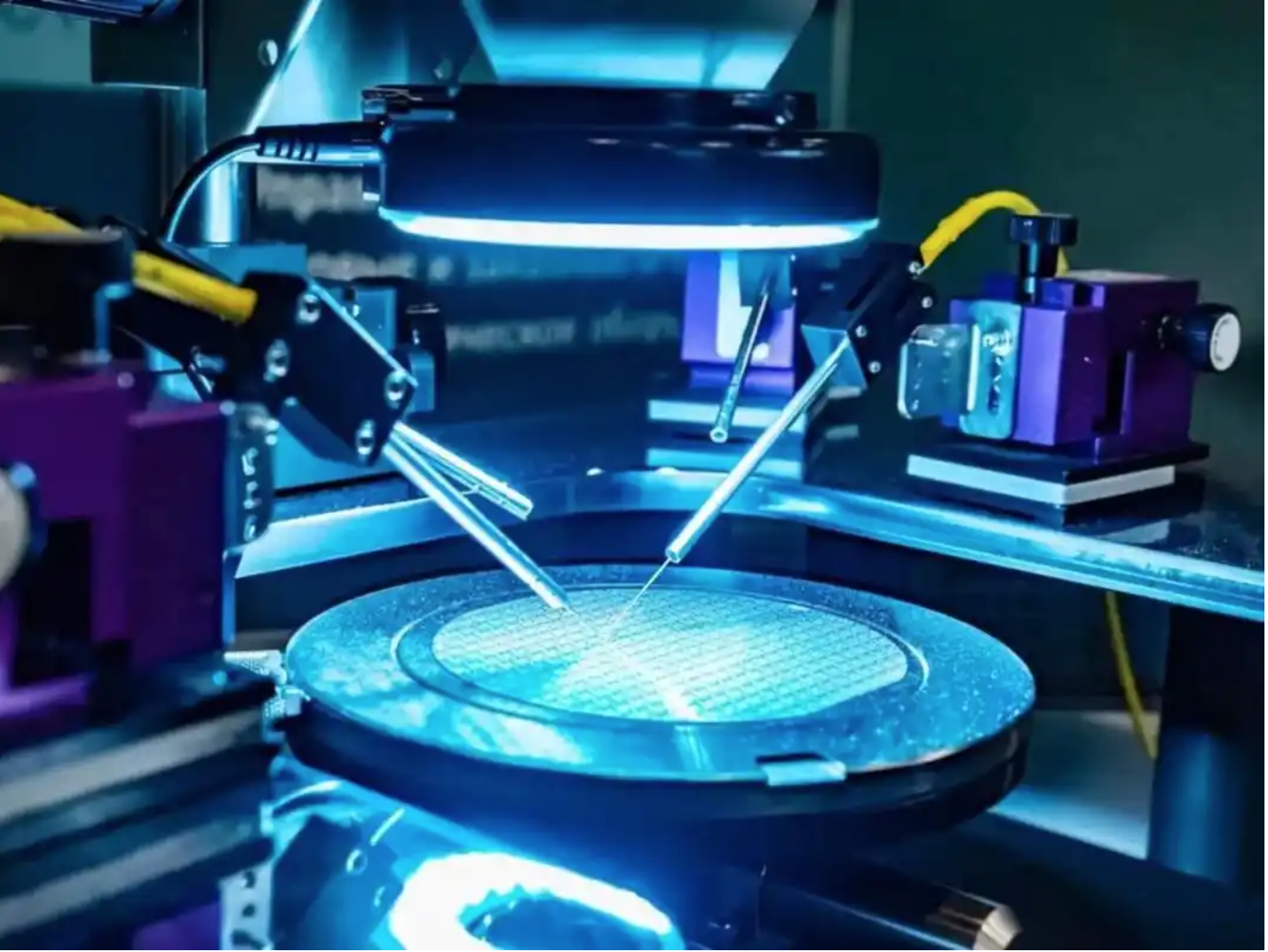

應材近日發表針對NMOS電晶體應用全新開發的Centura RP系列磊晶系統;所謂的NMOS電晶體是一種MOS電晶體,其活性載子(active carriers)是在p型矽基板上靜電形成的n通道中,流經n型源極與汲極區域的電子流。

根據Gartner的估計,在2012年,整體磊晶設備市場規模約5.9億美元,成長速度高于其余晶圓制造前段設備,而該趨勢可望持續發展。

Chu表示,磊晶沉積設備在過去十年有大幅度進展;應材在十年前就是該市場的領導者,市占率達八成,磊晶設備主要銷售給晶圓片供應商。但今日,因為該技術能改善行動處理器性能,應材因此售出更多系統,晶圓代工廠是最大的客戶群。

根據Chu指出,現在的半導體制程需要經過數個磊晶步驟,而且隨著晶片供應商認為該技術具備能改善其元件性能的潛力,未來的需求將會更大。應材將磊晶定義為沉積或是生長單晶矽薄膜,該沉積薄膜呈現晶格架構且與基板的方向一致。

Chu指出,在PMOS磊晶制程之外再布置一道NMOS磊晶制程,能讓晶圓代工廠進一步改善下一代元件的性能;這種新的制程已經獲得數家客戶采用。

自90奈米節點以來,采用以原位摻雜(in-situ doping)的應變選擇性磊晶薄膜(strained selective epi film),就可改善電子遷移率并降低PMOS電晶體內的電阻,提升晶片速度;Chu表示,在NMOS電晶體提供選擇性磊晶,也能達到類似的效果并加強整體晶片性能。

「人們正在尋找下一個能帶來優勢的應用領域,」Chu指出,新的磊晶材料會是電晶體在20奈米以下制程速度提升的關鍵推手

評論