Xilinx UltraScale 架構—業界首款ASIC級All Programmable架構

通過UltraScale架構提供的高布線效率從根本上完全消除了布線擁塞問題。結果很簡單:只要設計合適,布局布線就沒有問題。這樣也使器件利用率達到90%以上,且不降低性能或增加系統時延。

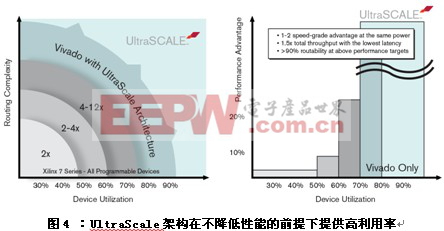

本文引用地址:http://www.104case.com/article/147355.htm下面的這兩幅圖顯示出UltraScale架構以及Vivado設計套件的相應改進對于系統性能和器件利用率的改善效果。與競爭產品PLD 架構相比,UltraScale架構將利用率和性能提升到了全新的高度,無需像PLD架構那樣為了實現設計目標,不得不在利用率、性能、時延和延長布局布線時間等方面進行權衡取舍。

?

?圖4中左圖的藍綠色區域表示:如果系統設計適合使用UltraScale器件,那么就可以布線,而且不受設計復雜性和器件利用率方面的制約。左圖中的灰色區域表明Vivado設計套件在任何利用率水平下的運行速度都比競爭設計工具快2至12倍。兩幅圖的藍綠色區域都表明Vivado 設計套件是唯一可以在高器件利用率條件下對大型復雜系統設計進行布局布線的工具。同時,右圖的灰色區域顯示采用Vivado設計套件創建出設計的速度在任何利用率等級下都比競爭產品快25%。UltraScale架構可支持海量數據流與布線,Vivado設計套件與之結合使用,能夠在競爭產品無法企及的設計空間內提供更高的系統性能。

UltraScale架構3D集成可增強所有功能

最新Virtex? UltraScale和Kintex? UltraScale系列成員產品能使賽靈思第二代3D IC架構中的連接功能資源數量及相關晶片間帶寬實現階梯式增長。布線、帶寬和最新3D IC大容量存儲器優化接口容量的顯著增加能確保新一代應用在極高的利用率水平下實現目標性能。

實現快速、智能處理

從噪聲中提取更多信號,創建更加逼真的畫面,以及應對無止境的數據包流量增長,所有這些都在對智能處理性能提出更高要求。與此同時,還要將成本控制在規定的預算范圍內,這樣就給設計帶來了諸多實際限制。簡言之,市場需要以更少的成本實現更高的系統性能,這是大多數電子產業永恒不變的趨勢。而賽靈思的UltraScale器件非常適合滿足這些多元化的設計要求。

最新的27x18位乘法器和雙加法器以及關鍵路徑優化功能顯著提升了定點和IEEE 754標準浮點算法的性能與效率。UltraScale架構能夠讓雙精度浮點運算的資源利用率實現1.5倍的效率提升,并具有更多的DSP資源數量,因此可以滿足新一代應用在TMAC處理性能和集成方面的要求,并實現最優價格點。

UltraScale架構經過專門優化,可解決以數百Gbps速率運行的包處理功能有關的關鍵路徑瓶頸問題,這些功能包括:誤差校正與控制(ECC)、循環冗余校驗(CRC)以及前向糾錯(FEC)。增強型DSP子系統,與硬化的100 GbE MAC和Interlaken接口以及賽靈思SmartCore 包處理與流量管理IP完美結合在一起,采用最佳封裝,能夠實現線速高達數百Gbps的包處理功能。

提供海量I/O和存儲器帶寬

UltraScale架構能在顯著增強高速SerDes收發器性能的同時大幅降低其功耗。Virtex UltraScale器件采用可支持5 Tbps以上串行系統帶寬的新一代SerDes(收發器)。ASIC級SerDes的靈活性要高于早期器件中的SerDes,同時保留了前代產品可靠的自適應均衡功能(自動增益控制、連續時間線性均衡、判定反饋均衡以及sliding 滑動DFE)。賽靈思的自適應均衡功能可將誤碼率維持在無法察覺的水平(<10?17)并允許UltraScale SerDes直接驅動每秒高達數GHz的高速背板。

賽靈思UltraScale架構集成了多個DDR3/4-SDRAM存儲控制器以及硬化的DDR物理層(PHY)片上模塊,從而將存儲器接口功能推向一個全新高度。UltraScale器件包含:

· 更多SDRAM控制器

· 更廣泛的SDRAM端口

· 更快的存儲器端口

硬化的SDRAM PHY模塊與軟核PHY相比能夠將讀取時延降低30%,同時它具有控制DDR4 SDRAM的能力,可將外部存儲器功耗降低20%以上。

片上模塊RAM(BRAM)經重新構建后可與系統中其它可編程模塊性能相匹配并降低功耗。利用新的架構特性,設計人員無需使用其它片上布線或邏輯資源就能高效創建出大規模快速RAM陣列和FIFO。

UltraScale架構滿足新一代系統的系統級功耗要求

每一代All Programmable邏輯器件系列都能顯著降低系統級功耗,UltraScale架構正是建立在這一傳統優勢之上。低功耗半導體工藝以及通過芯片與軟件技術實現的寬范圍靜態與動態電源門控可將系統總功耗降低至賽靈思7系列FPGA(業界最低功耗的All Programmable器件)的一半。

評論