通過(guò)增益校準(zhǔn)提高DAC積分非線性(INL)

在正常操作期間,如果傳到DAC的數(shù)字代碼小于中間點(diǎn),轉(zhuǎn)換前使用第一個(gè)增益校準(zhǔn)值來(lái)修正。如果傳到DAC的數(shù)字代碼大于中間點(diǎn),轉(zhuǎn)換前使用第二個(gè)增益校準(zhǔn)值來(lái)修正。通過(guò)更新圖3所示的gain trim registers(增益調(diào)整寄存器)校準(zhǔn)即時(shí)完成。使用SoC里面的直接存儲(chǔ)器存取(DMA)模塊,寄存器更新速度會(huì)更快。

本文引用地址:http://www.104case.com/article/135954.htm在全范圍中間改變?cè)鲆嫘拚禃?huì)產(chǎn)生調(diào)整偏移(見(jiàn)方程3)。這個(gè)調(diào)整偏移需要在算法的后半部分來(lái)補(bǔ)償 (見(jiàn)圖5)。

![]()

結(jié)果

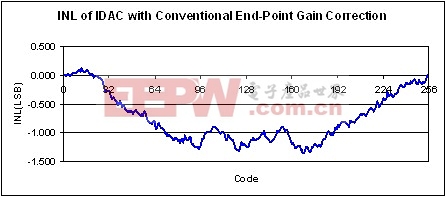

我們來(lái)做個(gè)比較,使用傳統(tǒng)終端校驗(yàn)的8位電流DAC(iDAC)沒(méi)有實(shí)施我們所講的算法之前測(cè)量的INL性能,INL大約為1.5 LSB,如圖6所示。

圖6:使用傳統(tǒng)終端增益校驗(yàn)IDAC的INL

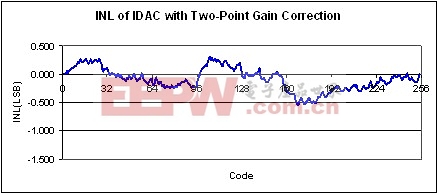

使用該算法后,INL現(xiàn)在降到0.8LSB,如圖7所示。

圖7:使用兩點(diǎn)增益校準(zhǔn)IDAC的INL

結(jié)論

我們介紹了SoC中用于提高DAC積分非線性 (INL)的固件技術(shù)。并以PSoC® 3為例進(jìn)行了驗(yàn)證。對(duì)于PSoC® 3中的電流和電壓DAC,該方法可以使INL改善85%。

評(píng)論