富士通半導體交付55nm創新方案

CS250S是一項革命性的創新技術,通過全新設計的DDCTM(Deeply Depleted Channel™) 晶體管技術,可以將現有65nm的功耗降低到原來的一半,而性能不受到任何影響,同時可很好地改善工藝生產造成的功耗波動。

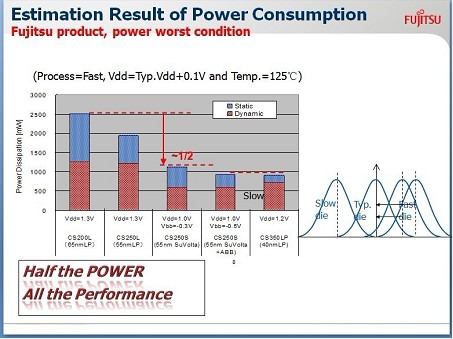

本文引用地址:http://www.104case.com/article/134219.htm如下圖5所示,在fast corner的最壞情況下,采用CS250S(55nm)的工藝制程其靜態功耗和動態功耗均比采用65nm工藝制程降低50%,而且fast corner和slow corner更加集中,對于封裝熱阻的考慮變得更加收斂。

圖5:富士通半導體最新55nm工藝CS250S功耗比65nm降低一半。

完整、經過驗證的一站式IP平臺

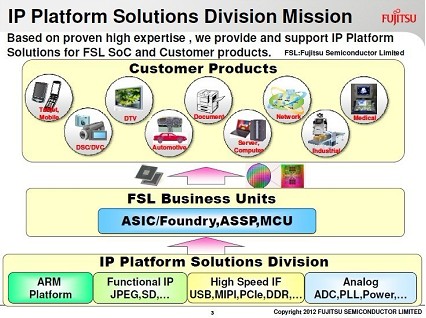

前文曾指出,SoC的成功除了選擇合適的工藝制程外,有競爭力的IP也是關鍵。客戶的SoC中要用到各種不同的IP,尤其當遇到與工藝制程相綁定的模擬IP的時候,選擇就不是那么的靈活,而富士通半導體完整的,經過驗證的低功耗模擬IP,可以為SoC設計帶來福音。

早在上世紀90年代,富士通半導體就在中國大陸開始推廣ASIC方案和設計服務,最初客戶以通訊和網絡IC公司為主。2006年,該公司又在中國開始推廣其日本代工廠的COT服務,以便為中國客戶提供90nm和65nm工藝的ASIC設計、IP、晶圓代工等多元化的服務,很多應用如衛星電視、CMMB等消費類應用芯片都是在富士通日本晶圓廠投片生產的(40nm以下設計是轉由臺積電代工)。從2008年開始起, 他們中國客戶中消費類電子IC廠商的比重逐年升高。

安佛英明在演講中指出:“上市時間是消費類終端芯片產品取得成功的最重要因素,而迅速地整合IP資源是達到這一訴求的關鍵。富士通半導體提供非常完整的針對這類應用芯片的解決方案,提供諸如USB、HDMI、PCIE、SATA、MIPI、ARM CPU、AD/DA、電源管理等諸多經過嚴格評估和量產驗證的IP。而這些IP大部分都是富士通內部開發的,如此省去了客戶為尋找各個IP而去和不同IP供應商談判的時間。從芯片的風險角度來講,一旦芯片出現IP的質量問題,客戶也無需為此而在各個IP供應商之間周旋。從成本角度,富士通半導體所提供的打包IP方案也會幫助節省客戶初期的IP 投入。”

圖6:富士通半導體可提供完整、經過制造驗證的高品質IP

評論