富士通半導體交付55nm創新方案

CS250L和CS250S的推出可以說恰逢其時,使得中國消費電子IC廠商又多了一種選擇,可不用急于往40nm節點冒進,在實現接近功耗的同時不僅能保護現有在65nm上的IP投資,而且NRE的費用仍像65nm一樣處于能承受的水平,因此非常適合中國的國情。

本文引用地址:http://www.104case.com/article/134219.htm使65nm IP可直接用于55nm工藝

“模擬IP是通往真實世界的接口,但是大家都知道模擬IP的使用和工藝制程是非常相關的,比如一個IP在65nm的工藝制程下能用,可是到了55nm的時候就要換基于55nm工藝的IP了。富士通半導體解決了這個問題,憑借我們在模擬IP方面多年的技術積累,我們的65nm工藝IP可以直接用于55nm工藝中,這就極大地保護了客戶投資。” 劉哲表示。“另外,從晶圓代工、IP授權、設計服務以及封裝測試,富士通半導體強調的是一站式增值設計服務,可將客戶的成本、風險、上市時間降至最低。”她補充道。

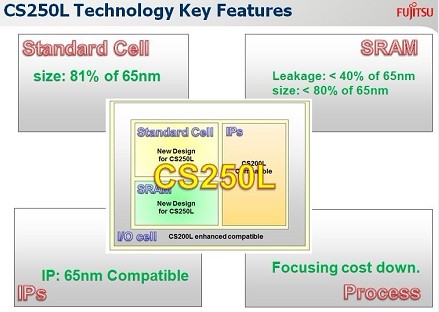

富士通半導體的上述兩套全新55nm工藝是基于65nm技術而開發,可使客戶保護以往的投資。其中CS250L是基于對現有65nm后端工藝而優化的全新標準單元、SRAM,可使整體功耗降低20%,芯片面積則節省15%左右。最大的特點是全套65nm IP不需要重新做移植,GDSII網表可以直接使用。圖3展示了CS250L的關鍵優勢。

圖3:CS250L的關鍵優勢。

以55nm工藝提供接近40nm的功耗

以55nm工藝提供接近40nm的功耗,同時還不會降低性能,理論上講這似乎不太可能。不過富士通半導體和美國SuVolta公司合作開發的新制程CS250S使得“Half the POWER,All the Performance”變成現實。

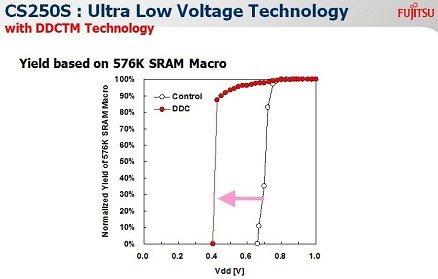

過去,雖然芯片的工藝制程技術一直在飛速進步,不過自從進入0.18微米(180nm)時代,CPU核心電壓降至1.xV級別后,即使是目前實際生產用最新的28nm制程也只能使核心電壓維持在1V左右。“高”電壓帶來的功耗問題也使移動計算方面處處受限,目前智能手機、平板電腦等最大的問題之一就是功耗和續航。而芯片電壓之所以無法突破1V的重要原因之一就是低壓無法驅動內部的SRAM模塊。

使電壓閾值下降至0.4V左右。DDCTM晶體管制造的嵌入式576Kb SRAM模塊最低可在0.425V電壓下工作,相比目前常用SRAM最低0.7V左右的工作電壓減少了40%左右。相對于效果類似的ETSOI和Tri-Gate制程,富士通半導體的這種技術更加簡便易行。富士通半導體應客戶要求將低功耗特性全面導入對應的產品中,對于逐漸SoC化的移動處理器來說這絕對是個好消息。

圖6顯示了576k SRAM宏模塊在不同電壓下的良率。良率由所有比特都通過的宏模塊數目計算而得。

圖4:576k SRAM宏模塊在不同電壓下的良率。

評論