關于Micron和Intel 20nm 64-Gbit MLC NAND閃存的深度探究

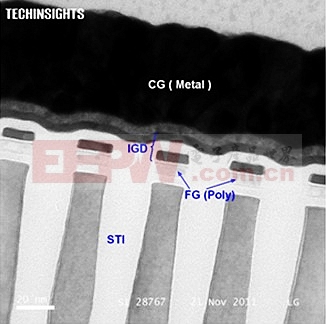

電荷捕捉閃存(CTF)曾被視為另一種選擇,因為它擁有平面化的單元結構。不幸的是,我們至今都沒有看到它在NAND產品中成功問世。在目前以浮柵為基礎的NAND閃存技術條件下,有一種可能的解決方案可用于在20nm節點下進一步縮減NAND閃存的尺寸,即把金屬作為控制柵與高K柵極絕緣層(IGD)結合在更薄的浮柵上。

本文引用地址:http://www.104case.com/article/133125.htm

平面浮柵NAND(IMFT20nmNAND閃存)

工藝中的關鍵技術和新的閃存單元結構

在此類極小的閃存設備上難以使用一些傳統的浮柵單元結構。IMFT中具有平面化單元結構的20nm技術,以及先進的工藝技術解決了這一重要難題。

- 將多晶硅控制柵(CG) 填入更窄的鄰近浮柵間隙

- 單元與單元間的干擾

- 絕緣膜(IPD)的縮減限度和小型控制柵與浮柵的耦合率

為了制造出20nm NAND單元,在光刻步驟中采用了先進的單元間距縮小技術(例如雙重成像技術)。20 nm以下設計規則的圖形刻畫,也將運用四重成像技術來克服193nmArF沉浸式雙重成像技術的局限。但這些可能還遠遠不夠,因為處理這種圖形刻畫所要求的極紫外光刻(EUV)工具對閃存生產來說太過昂貴。這種NAND元件的單個閃存單元字線和位線方向各自大約40-nm,單元物理面積為0.0017µm2,這種單元可能是所有NAND產品中最小的。該NAND器件采用了平面化浮柵架構,搭配薄型多晶硅浮柵,高介電常數的IGD和金屬控制柵。

在這種全新的單元架構中,氧-氮-氧(ONO)的柵間絕緣層被高介電常數的IGD替代,從而還原了在平面單元架構中應當減小的浮柵與控制柵的耦合率。更薄型的多晶硅浮柵技術被用來降低單元間的干擾。金屬柵字線是指通過使用硬掩模層來刻畫多柵極堆棧結構。單元間距被大幅縮減之后,單元間的耦合電容增加將會是個很嚴重的問題,因為單元間的干擾增加會降低單元性能,可靠性也成問題。為了解決這些難題,同時在單元柵極之間和第一層金屬位線間運用了一種空氣絕緣工藝,把氣隙架構用作低介電常數的空隙填充材料。位線接觸孔的錯位布局獲得了更好的光刻工藝裕量,并且一個NAND串上有68個字線。

新單元架構結合了IMFT 20nm多層單元閃存中的關鍵集成技術,具有非常廣闊的前景,它可以通過單元尺寸的大幅縮減來進一步延長傳統柵極閃存的使用壽命。但是,進一步縮減柵極結構,將會導致電子俘獲急劇減少,從而需要在十幾nm的多層單元閃存中控制20個以下的電子。正因為這樣,一些新穎的器件理論和替代解決方案,例如IMFT的最新NAND閃存器件中所采用的方案,已經做好了在不遠的將來替代NAND閃存的準備,這也是由于居主導地位的移動應用對器件尺寸的需求和穩定性的挑戰將會更高。近期來看,在NAND產品中見到的結合了3-D構造的電荷捕捉閃存就可以作為替代目前平面化NAND閃存技術的另一種可行選擇,與此同時,大量的新型存儲理念也開始涌現并且爭奪作為NAND閃存替代品的地位。浮柵NAND閃存雖然目前還沒有,但最終會達到它的尺寸極限。在不遠的將來,看看IMFT以及其他閃存制造企業將如何變革去克服這些尺寸極限,將會非常有趣。

評論