關(guān)于Micron和Intel 20nm 64-Gbit MLC NAND閃存的深度探究

NAND閃存在半導(dǎo)體市場上的成功主要得益于手機(jī)和平板電腦市場的持續(xù)迅猛發(fā)展以及高性能固態(tài)硬盤(SSDs)取代硬盤驅(qū)動器的廣泛應(yīng)用。美光與英特爾去年共同宣布,通過20 nm制造工藝技術(shù)結(jié)合突破性的單元架構(gòu)概念,可以制造出僅由一組簡單芯片組成的TB容量NAND閃存。

本文引用地址:http://www.104case.com/article/133125.htm過去幾年,NAND閃存因為出色的物理擴(kuò)展性和每個單元兩到三個字節(jié)的多層單元(MLC)搭載方式,在眾多高密度商業(yè)內(nèi)存中享譽(yù)最高。然而近期便攜式電子產(chǎn)品對于NAND閃存的大量需求,導(dǎo)致NAND閃存必須大幅縮小器件架構(gòu)以獲得更高的密度和更快的速度,并消耗更低的單字節(jié)成本。NAND閃存單元尺寸的大幅縮減在傳統(tǒng)的20 nm級浮柵閃存單元架構(gòu)下,必然會遇到巨大障礙。

面對以上提及的這些難題,英特爾與美光負(fù)責(zé)工藝制程開發(fā)的合資公司——英特爾美光閃存科技(IMFT)一直在積極尋求縮小NAND單元尺寸的方法,并最終成功開發(fā)和制造了第一個20nm設(shè)計規(guī)格下的高密度多層級NAND閃存。通過全平面浮柵單元設(shè)計的引入,IMFT也發(fā)明了全新的閃存架構(gòu)。作為公認(rèn)的NAND閃存制造工藝業(yè)內(nèi)的領(lǐng)軍企業(yè),IMFT引入了結(jié)合高K/金屬柵(HKMG)疊層技術(shù)的單元架構(gòu)平坦化工藝。這種工藝可以攻克在20 nm及以下尺寸縮減過程中面臨的許多物理和電子方面難題。

為了更好的了解這種先進(jìn)的工藝和全新的單元架構(gòu),UBM TechInsights(http://www.ubmtechinsights.com/

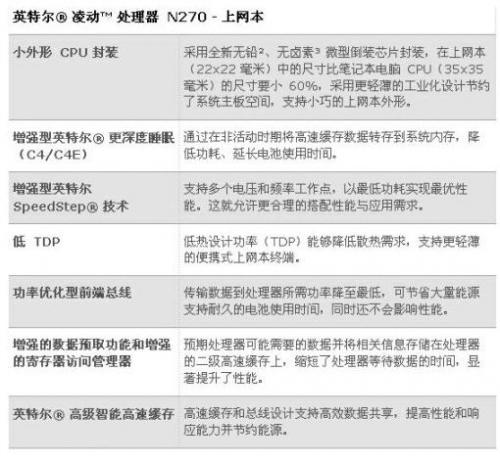

在64-Gbit多層單元NAND閃存的制造過程中,20 nm加工技術(shù)的引入讓IMFT奠定了在新制程節(jié)點中的領(lǐng)導(dǎo)地位。這種NAND芯片面積只有117 mm2,比IMFT現(xiàn)存的25 nm 64 Gbit NAND閃存在面積上減少了近30%,這成為其一大特色。IMFT的64-Gbit NAND閃存是由單層多晶、金屬柵和三層金屬制造的,呈48-pin無鉛TSOP封裝。64-Gbit閃存單一芯片分成四個bank加上一個單邊焊盤,與之前芯片面積為162 mm2的25 nm 64 Gbit NAND閃存相比,存儲區(qū)效率達(dá)到了52%。

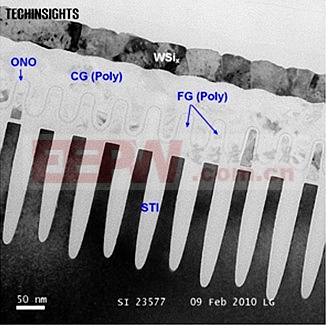

在傳統(tǒng)的NAND浮柵單元上,控制柵(CG)和絕緣膜纏繞在浮柵(FG)上,耦合系數(shù)很大程度上依賴于浮柵側(cè)壁,如下圖所示:

傳統(tǒng)浮柵NAND(IMFT 25 nm NAND閃存)

深度探究

對于20nm級及其以下的工藝節(jié)點來說,單元空間已經(jīng)很窄,控制柵無法插在浮柵之間。因此,NAND閃存只能采用平面化單元的結(jié)構(gòu),而不再讓控制柵和浮柵纏繞在一起。

評論