采用硬件加速發揮MicroBlaze處理能力

不過客戶仍不滿意,客戶要求更高的速度。在這種情況下,把算法從浮點運算變為固點運算并不適合。因此,我們開發了一款新型專用硬件加速器(新型FSL IP)來加快對循環的處理。

本文引用地址:http://www.104case.com/article/106702.htm

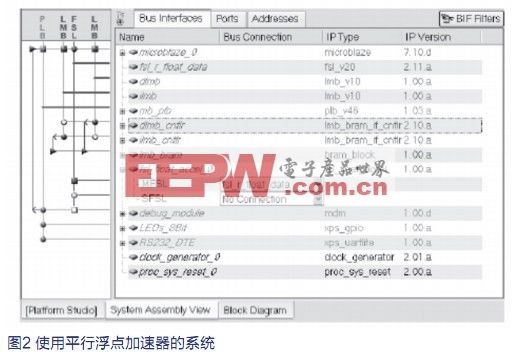

新的FSL IP使用CORE Generator模塊浮點_v4_0來為4x ADD、2x MUL、1x GREATER、1x LESS和1x SQRT等操作創建9個示例。所有這些示例都可以實體化,并對相同的輸入數據進行完全并行處理(圖2)。

FSL IP中實例的創建帶有部分時延,但吞吐率僅為1。這要求為加速器內部的控制器硬件準備更多的芯片,不過這樣可以在每個時鐘周期內向協處理器提供新數據。

在取回結果前,只有在處理循環末端才需要增加周期。

我們采用直連方式把MicroBlaze連接到FSP IP時不需要FIFO。傳輸的所有數據都將緩存在IP內,并隨即加以處理。

從FSL IP返回到MicroBlaze的連接是使用FSL總線創建的。由于我們必須發回一些結果,因而這更加容易實現,而且可以更加簡單地在IP內完成。部分CoreGen模塊有一些已被添加到執行時間中的時延,并被getfsl()調用完全覆蓋。MicroBlaze只需要等到所有結果都存入FSL總線FIFO。不過,只要數據率是1,即可完全實現所要求的吞吐率。

FSL總線的額外延遲僅會占用為數不多的一些周期。使用FSL硬件加速器的C代碼如下:for (i=0;i<512;i++) {

putfsl(farr[i],fsl0_id);

}

// get the min,max values:

getfsl(min_f,fsl0_id);

getfsl(max_f,fsl0_id);

// get the sum and products:

getfsl(f_sum,fsl0_id);

getfsl(f_sum_prod,fsl0_id);

getfsl(f_sum_tprod,fsl0_id);

getfsl(f_sqrt,fsl0_id);

算法的最終實施僅需大約4,630個周期,而且依然是全浮點實施。

硬件需要本來應該用于實施硬件加速器的更多芯片才能并行計算出所有結果。不過與擴展FPU實施方案相比,我們最終提升了大約7.6倍。否則,如果使用標準處理器來替換這個50MHz的處理器,可能需要大約380MHz的CPU才能勝任(假設硬件自帶有浮點平方根函數)。

更為顯著的是與使用PFU的最初方案,而非平方根函數的對比效果:總體提升了大約239倍。這種效果可能需要12GHz左右的浮點處理器才能實現。

評論