小芯片聯盟成立,大陸芯片“危”?

來源:星海情報局

該標準專為小芯片(chiplet)而設置,旨在為小芯片互連制定一個新的開放標準,簡化相關流程,并且提高來自不同制造商的小芯片之間的互操作性。

美國國防部高級研究計劃局(DAPRA)在2017年8月啟動“通用異構集成及IP復用策略(CHIPS)”項目,這是DAPRA總投資15億美元的“電子復興計劃(ERI)”中的一部分,意在促成一個可兼容、模塊化、可重復利用的小芯片生態系統。

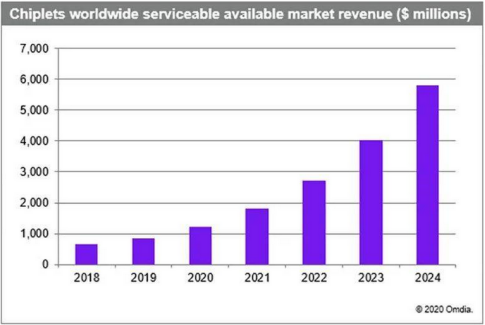

知名市場研究機構Omdia預測,小芯片將在2024年全球市場規模擴大到58億美元,較2018年的6.45億美元增長9倍。到2035年,小芯片市場規模有望增至570億美元。

來源:Omdia

來源:Omdia 什么是小芯片?

什么是小芯片?

摩爾定律的出現設定了極為關鍵的技術發展節奏基準,極大地推動了當時在前進中迷茫的半導體產業。

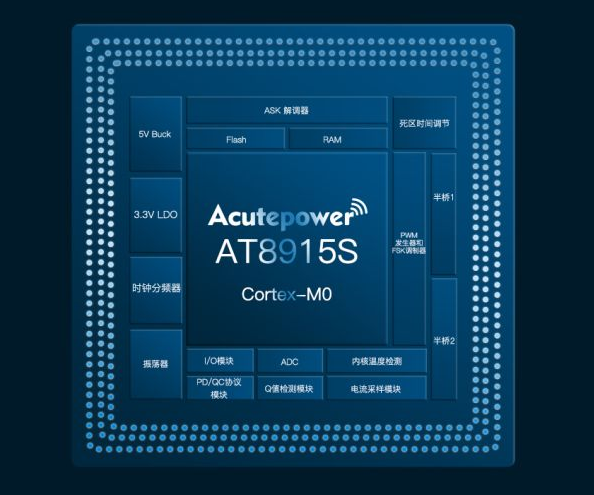

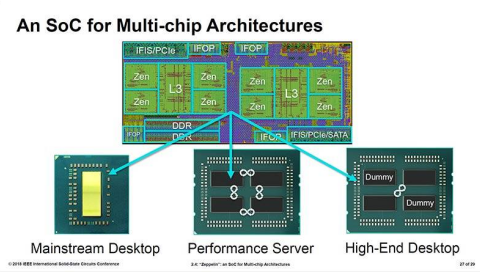

SoC本質上是一種芯片的集成,例如我們常說的手機處理器,其實就是CPU、GPU等芯片的集成,也是一種SoC。

這種技術的優勢在于提高模塊之間通信速度的同時,還能夠做到低功耗、低成本。

2001年:芯片制程工藝是130nm,當時非常流行奔騰3處理器。2004年:90nm的元年。2012年:制程工藝發展到22nm,此時聯電、聯發科、格芯等很多廠家可以達到22nm的半導體制程工藝。 2015年:芯片制成發展的一個分水嶺,進入14nm時,聯電止步于此。2017年:步入10nm時代,英特爾停在了10nm,i5和i7處理器由于良率問題而遲遲無法交貨。2018年:7nm來臨,英特爾至今無法突破,而美國另一家芯片代工巨頭“格芯”,也在7納米處倒下。2019年:6nm開始量產。2020年:制程開始進入5nm時代,進入更難的5nm,只有三星和臺積電生存下來了,但三星被爆出良品率造假。

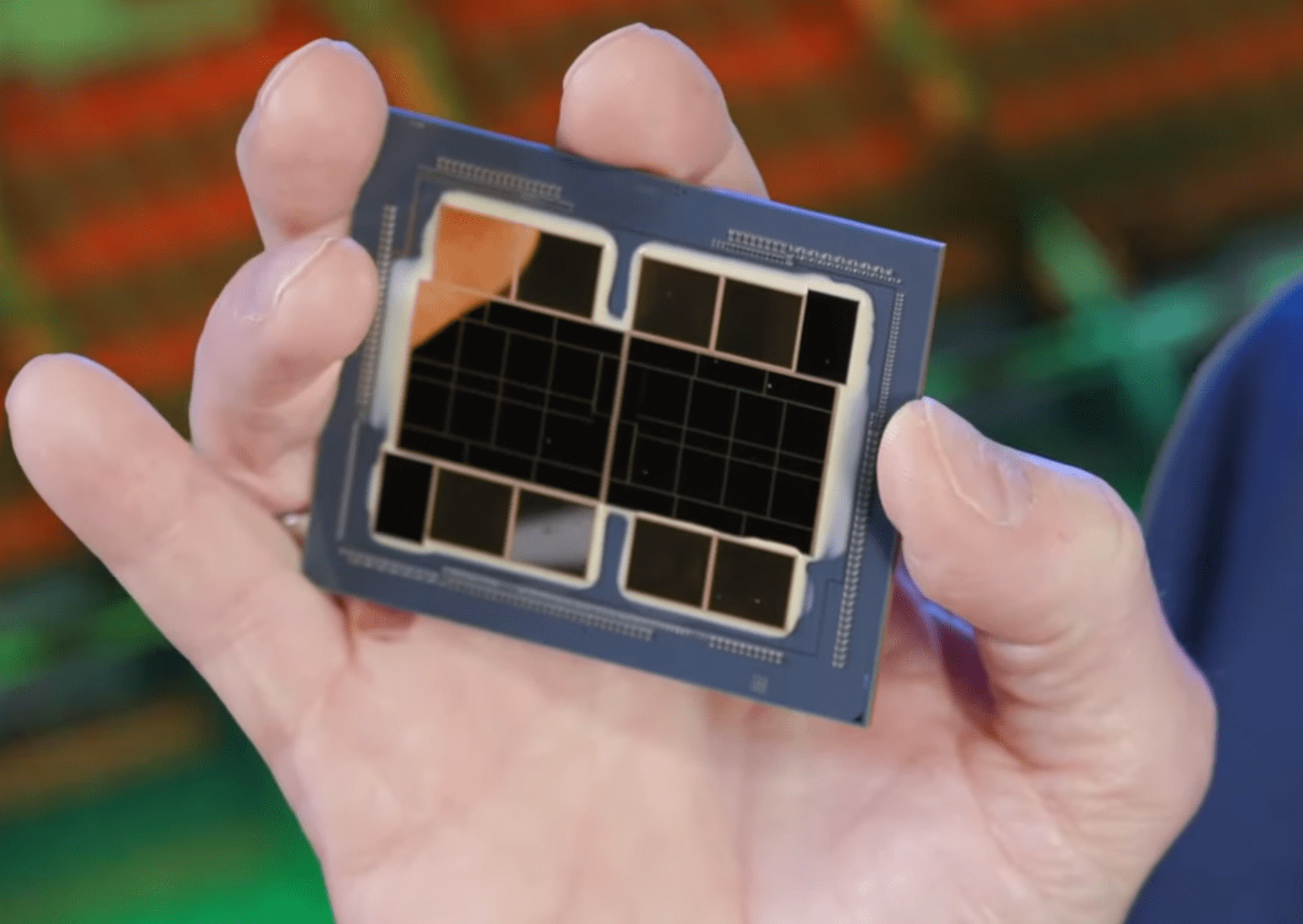

近幾年隨著頭部廠商帶頭投入更多經歷到小芯片的研發當中,小芯片技術也逐步從實驗室走向實踐。

小芯片聯盟為何成立?

小芯片聯盟為何成立?這帶來的好處是,7nm制程部分的芯片面積大幅縮減,而采用更成熟制程的I/O模塊有助于整體良率的提升,進一步降低晶圓代工成本。

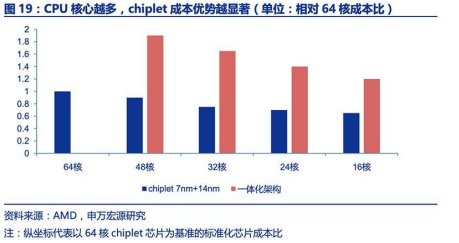

綜合來看,CPU核心越多,小芯片組合的成本優勢越明顯。

理想狀態下,借助小芯片方法,芯片設計公司只需專注于自己擅長的IP,而不必擔心其余IP,既有助于提升核心創新能力,又經由多種IP設計分攤了研發成本。

此外,小芯片可以充當異構處理器,將GPU、安全引擎、AI加速器、物聯網控制器等不同處理元素按任意數量組合在一起,為各類應用需求提供更豐富的加速選擇。

隨著小芯片的優勢逐漸顯露,它正被微處理器、SoC、GPU和可編程邏輯設備(PLD)等更先進和高度集成的半導體設備采用。

但小芯片技術要走向成熟,還需要面對諸多挑戰。

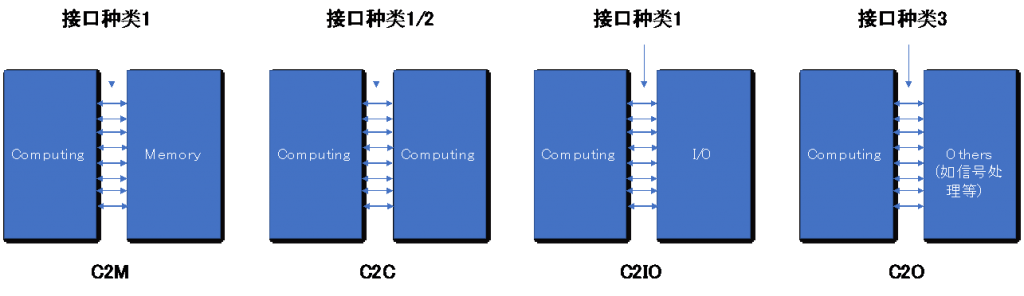

在小芯片技術中,采用die to die的鏈接方式,各裸片互連必須考慮到互連接口和協議。

在設計中必須要考慮到工藝制程、封裝技術、系統集成、擴展等諸多復雜因素。同時,還需要滿足不同領域對信息傳輸速度、功耗等方面的要求。

這使得小芯片的設計過程變得非常復雜,而其中橫在小芯片面前的最大難關來自于沒有統一的協議。

Marvell(美滿,前邁威科技)曾經在2015年推出了MoChi架構這一小芯片模型。此后Marvell就陷入了選擇接口的困難中。根據Marvell CTO Yaniv Kopelman表示,由于不想堆高封裝成本或是被單個供應商綁定,他們不想使用內插器或者InFO類型的封裝。

另外,使用小芯片的時候必須在中間劃分IP,但在哪里劃分以及如何開發架構也對最終產品的實現提出了挑戰。

Yaniv Kopelman總結到:“在演示中構建IP很容易,但從演示走向生產還有很長的路要走。”

在過去很長一段時間內,小芯片一直備受芯片設計行業關注。越來越多的廠商開始使用小芯片,這使得小芯片越來越普遍。制造商們希望小芯片解決芯片制造目前面臨的制造成本、擴展性等多方面的問題。

但由于缺少統一的標準,小芯片此前的協議十分混亂。

這樣的情況下,芯片制造商們無法實現他們的終極構想:連通不同架構、不同制造商生產的裸片,根據不同場景進行定制。

小芯片聯盟的出現正是希望通過集結各個廠商之力,推出統一的標準,規范小芯片的協議。

UCIe標準的全稱為“Universal Chiplet Interconnect Express”(通用小芯片互連通道),在芯片封裝層面確立互聯互通的統一標準。

UCIe 1.0標準定義了芯片間I/O物理層、芯片間協議、軟件堆棧等,并利用了PCIe、CXL兩種成熟的高速互連標準。

該標準最初由Intel提議并制定,后開放給業界,共同制定而成。

事實上,英特爾新任總裁Pat自2021年上任以來一直強調英特爾要走IDM2.0的道路,在芯片制造上繼續深耕的同時還要具有更高的開放性,現在看來,當時英特爾可能就在暗指小芯片。

在2月18日的英特爾投資者大會上,英特爾宣布將為選擇其旗下IFS服務代工的客戶提供x86架構和其他類型內核混搭的可能性,這以一過程中可能就會用到小芯片技術。同時英特爾還在該大會上披露正在致力于打造一個“開放、可選擇、值得信賴”的開放生態圈。

如今這個巨頭們共同站臺的UCle1.0標準帶來的并不是技術革新,而是技術的標準化。這使得各廠商在使用小芯片時終于有了共同的規則。

以往的小芯片封裝都是各家廠商自行其是,在新的UCIe標準規范下,不同廠商的小芯片互通成為可能,允許不同廠商、不同工藝、不同架構、不同功能的芯片進行混搭,x86、ARM、RISC-V集成在一起也不是不可能。

小芯片聯盟將會怎樣影響芯片產業?

小芯片聯盟將會怎樣影響芯片產業?首先要明確的一點是,摩爾定律的逐漸失效其實對于中國的科技企業是一個彎道超車的機會,畢竟當其他公司都卡在技術瓶頸無法攻克時,中國企業卻在不斷追趕。

而小芯片聯盟所要做的事卻與此前各大廠家對SoC的“小修小補”截然不同,是一種推翻了全球范圍工人超過30年的行業制造標準,而開辟的新的天地,這不亞于從普通手機到智能手機的升級。

技術的革新也就勢必帶有行業的洗牌,玩家在芯片領域的話語權將重新排列,尤其是小芯片與SoC之間屬于相互替代的關系,所有電腦、手機廠商都要在二者之間做出二選一。

這其實本身對于國產芯片廠商來說是一個新的機會,因為目前小芯片也處于起步階段,中國企業與國際頭部企業差距其實沒有十分巨大。

但目前小芯片聯盟中其實并沒有任何一家大陸芯片企業,這也就意味著大陸企業實際上是被排除在規則制定之外的,在未來小芯片與SoC交輝的市場格局下,大陸其實非常需要一批反應迅速的玩家能夠及時切入小芯片賽道,率先完成基礎研究。

但問題在于即便大陸出現了小芯片相關企業或者有企業將精力投入到小芯片行業中,規則卻是由外國企業定制的,很難對大陸小芯片企業產生符合實際生產要求。

很多時候我們談中國制造的巔峰,是精確到小數點后面的好幾個0?還是7nm到5nm的突破?其實這些都只是一些簡單的數據,真正的中國制造巔峰是定制行業規則的能力,將產業以自己為核心凝聚在一起的能力,這也是國內大多數企業所缺乏的能力。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。