- 亮點: 設計規劃速度提升了10倍,實現速度提升了5倍,容量提升了2倍?–?它們共同使吞吐量加速了10倍 構建于全新的可擴展基礎架構、時序和解析優化引擎之上 已經在成熟和新興的技術節點上成功生產流片 為加速芯片和電子系統創新而提供軟件、知識產權(IP)及服務的全球性領先供應商新思科技公司日前宣布:正式推出將導致游戲規則發生改變的IC?Compiler?II,它是當前領先業界的布局和布線解決方案IC?Compiler?的繼任產品,可用于基于成熟和新

- 關鍵字:

Synopsys IC RTL

- 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS)日前宣布,已經達成了一項最終協議,收購以SystemC為基礎的高階綜合(HLS)與算法IP供應商Forte Design Systems。

- 關鍵字:

Cadence SystemC RTL

- 電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

- 關鍵字:

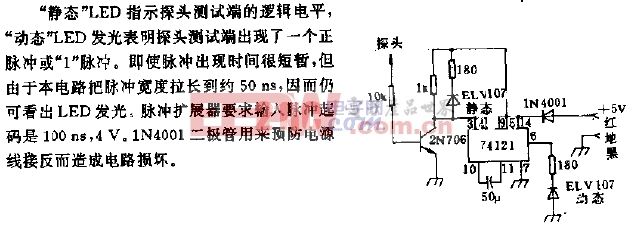

數字硬件 RTL 參數測試 JTAG

- 寄存器傳輸級(RTL)驗證在數字硬件設計中仍是瓶頸。行業調研顯示,功能驗證占整個設計工作的70%。但即使把重點放在驗證上面,仍有超過60%的設計出帶需要返工。其主要原因是在功能驗證過程中暴露出來的邏輯或功能瑕疵和

- 關鍵字:

RTL 時序邏輯 等效 檢查方法

- 在系統級芯片設計中,設計驗證是一項十分重要的工作。傳統的驗證方法雖然比較簡單,但對設計工程師要求很高,而且驗證時間過長。本文介紹開放式設計和驗證語言SystemC,通過該語言可實現RTL測試平臺的復用,降低驗證

- 關鍵字:

RTL 測試平臺 模型

- 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS),日前宣布推出最新版Cadence? Encounter? RTL-to-GDSII流程,面向高性能千兆級設計,包括在20納米最新技術節點上的新設計。這種最新的RTL-to-GDSII設計、實現與簽收流程是與領先的IP與晶圓廠合作伙伴及客戶合作開發的,能更有效地進行SoC開發,滿足并超越當今市場所需的功耗、性能與面積需求。

- 關鍵字:

Cadence RTL-to-GDSII

- 有限狀態機及其設計技術是數字系統設計中的重要組成部分,是實現高效率、高可靠性邏輯控制的重要途徑。大部分數字系統都可以劃分為控制單元和數據單元兩個組成部分。通常,控制單元的主體是一個狀態機,它接收外部

- 關鍵字:

RTL 策略 方案

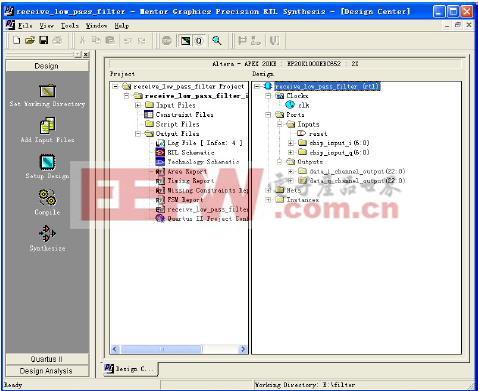

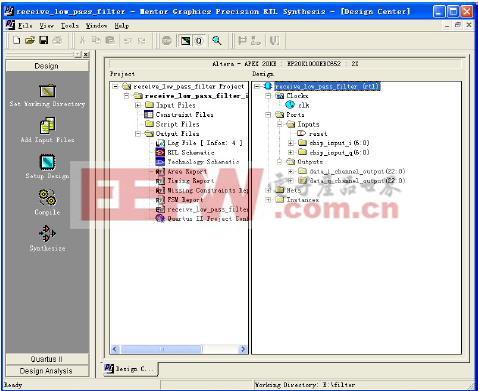

- 在FPGA設計中使用Precision RTL 綜合實例,數字濾波器通常分成有限脈沖響應(finite impulse response,也就是FIR)和

無限脈沖響應(infinite impulse response,也就是IIR)兩大類。FIR 濾波器相對

于IIR濾波器而言,優點是相位線性和性能穩定,應用范圍廣

- 關鍵字:

綜合 實例 RTL Precision 設計 使用 FPGA

- Synopsys日前宣布,在其Galaxy設計實現平臺中推出了最新的RTL綜合工具Design Compiler 2010,它將綜合和物理層實現流程增速了兩倍。Design Compiler自1988年問世以來,隨著工藝技術從1.5微米到32納米的進步,而不斷得到調整升級。而今時序與面積布線的優化已成為主要的挑戰,最新版工具與時俱進,針對拓撲技術進行擴展,為Synopsys布局布線解決方案IC Compiler提供“物理層指引”;將時序和面積的一致性提升至5%的同時,還將IC

- 關鍵字:

Synopsys RTL 32納米

- 全球領先的半導體設計、驗證和制造的軟件及知識產權(IP)供應商新思科技有限公司日前宣布:該公司在其Galaxy™設計實現平臺中推出了最新的創新RTL綜合工具Design Compiler 2010,它將綜合和物理層實現流程增速了兩倍。為了滿足日益復雜的設計中極具挑戰性的進度要求,工程師們需要一種RTL綜合解決方案,使他們盡量減少重復工作并加速物理實現進程。為了應對這些挑戰,Design Compiler 2010對拓撲技術進行擴展,為Synopsys旗艦布局布線解決方案IC Compile

- 關鍵字:

Synopsys Galaxy RTL

- 全球領先的半導體設計、驗證和制造軟件及知識產權(IP)供應商新思科技公司與中國內地最大的芯片代工企業中芯國際集成電路制造有限公司日前宣布,將攜手推出全新的65納米RTL-to-GDSII參考設計流程4.0(Reference Flow 4.0)。作為新思科技專業化服務部與中芯國際共同開發的成果,該參考流程中增加了 Synopsys Eclypse™ 低功耗解決方案及IC Compiler Zroute布線技術,為設計人員解決更精細工藝節點中遇到的低功耗和可制造性設計(DFM)等問題提供更多

- 關鍵字:

中芯國際 65納米 Galaxy RTL-to-GDSII參考設計流程4.0

- 2004年12月在一項由Synplicity公司委托的調查中,全世界超過20,000名開發者被詢問關于他們的硬件輔助ASIC驗證...

- 關鍵字:

FPGA ASIC NRE RTL

- 美國加州圣荷塞 2009年4月14日– 芯片設計解決方案供應商微捷碼(Magma®)設計自動化有限公司(納斯達克代碼:LAVA)日前宣布,該公司面向先進集成電路的全芯片綜合產品Talus® Design的最新版本正式面市。新版Talus® Design包括了一個增強的時序優化引擎、改善的內存使用效率以及先進的生產率改進,比如:創新性可用性、更為靈活的先進腳本語言以及領先的第三方可測性設計(DFT)產品支持。同時,Talus Design與Talus Vortex相結

- 關鍵字:

Magma RTL DFT Talus

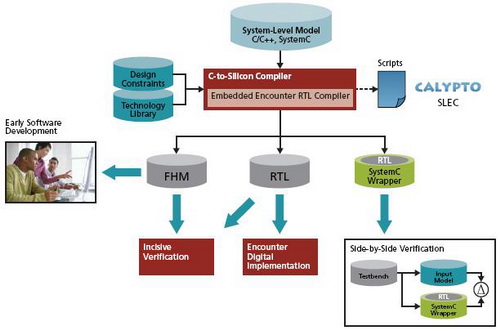

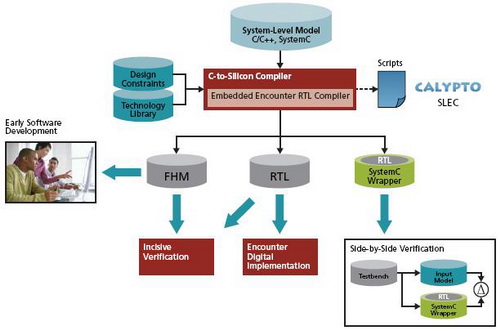

- 全球電子設計創新領先企業Cadence設計系統公司(納斯達克: CDNS),今天宣布推出Cadence® C-to-Silicon Compiler,這是一種高階綜合產品,能夠讓設計師在創建和復用系統級芯片IP的過程中,將生產力提高10倍。C-to-Silicon Compiler中的創新技術成為溝通系統級模型之間的橋梁,它們通常是用C/C++ 和SystemC寫成的,而寄存器傳輸級(RTL)模型通常被用于檢驗、實現和集成SoC。這種重要的新功能對于開發新型SoC和系統級IP,用于消費電子、無

- 關鍵字:

Cadence RTL SoC IP

- 全球電子設計創新企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布面向Common Platform™技術的45納米參考流程將于2008年7月面向大眾化推出。Cadence®與Common Platform技術公司包擴IBM、特許半導體制造公司和三星聯合開發RTL-to-GDSII 45納米流程,滿足高級節點設計需要。該參考流程基于對應Common Power Format(CPF)的Cadence低功耗解決方案,而且還包含來自Cadence的關鍵可制造性設計(De

- 關鍵字:

CADENCE Common Platform ARM RTL-to-GDSII 低功耗

rtl介紹

RTL是Real Time Logistics的縮寫, 意為:實時物流,是順應新經濟變革的當代物流理念,與現代物流理念區別在于,實時物流不僅關注物流系統成本,更關注整體商務系統的反應速度與價值;不僅是簡單地追求生產、采購、營銷系統中的物流管理與執行的協同與一體化運作,更強調的是與企業商務系統的融合,形成以供應鏈為核心的商務大系統中的物流反應與執行速度,使商流、信息流、物流、資金流四流合一,真正實現 [

查看詳細 ]

- 如何讀懂數字電路RTL設計?

- 深圳IC廠商誠聘資深數字IC設計工程師

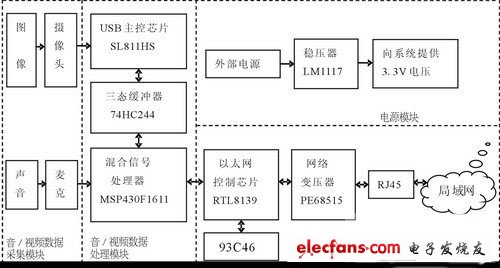

- KEIL,RTL,HTTP,DEMO,EASYARM2200,nbsp,nbsp,WEB KEIL-RTL HTTP-DEMO EASYARM2200

- MSP430,RTL8019 MSP430+RTL8019(新手上路,多多指教)

- Keil,ARM,RV,RTL,KIT 急切尋找 Keil ARM RV-RTL KIT ???

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473