- PLL鎖相環的基本結構及工作原理-PLL(Phase Locked Loop): 為鎖相回路或鎖相環,用來統一整合時脈訊號,使高頻器件正常工作,如內存的存取資料等。PLL用于振蕩器中的反饋技術。 許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步。

- 關鍵字:

pll 鎖相環

- 時鐘設備設計使用 I2C 可編程小數鎖相環 (PLL),可滿足高性能時序需求,這樣可以產生零 PPM(百萬分之一)合成誤差的頻率。高性能時鐘 IC 具有多個時鐘輸出,用于驅動打印機、掃描儀和路由器等應用系統的子系統,例如處理器、FPGA、數據轉換器等。此類復雜系統需要動態更新參考時鐘的頻率,以實現 PCIe 和以太網等其它諸多協議。 時鐘 IC 屬于 I2C 從器件,需要主控制器來

- 關鍵字:

I2C PLL

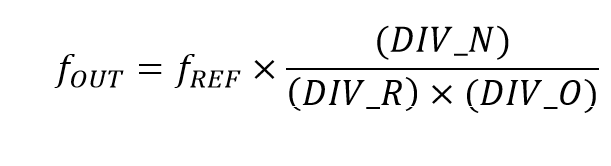

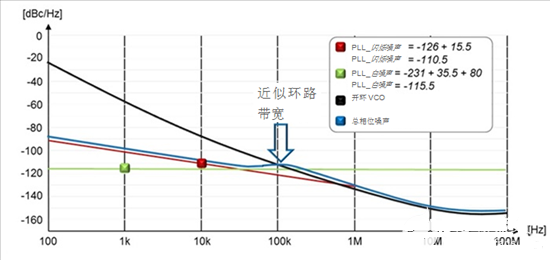

- 也許你也會跟我一樣認為典型數據表中的某些規格難以理解,這是因為其中涵蓋了一些你不太熟悉的隱含慣例。對許多RF系統工程師而言,其中一種規格便是鎖相環(PLL)中的相位噪聲。當信號源被用作本機振蕩器(LO)或高速時鐘時,相位噪聲性能對滿足系統要求起到了重要作用。最初從數據表中推斷出該規格時似乎就像一個獨立的項目。下面我來講解一下如何通過讀取PLL的相位噪聲規格來對您的無線電或高速應用可達到的性能進行初步評估。 注意,PLL是一種控制回路,這種系統具備頻率響應功能。參考路徑中生成的噪聲受控于回路中對系統輸

- 關鍵字:

PLL VCO

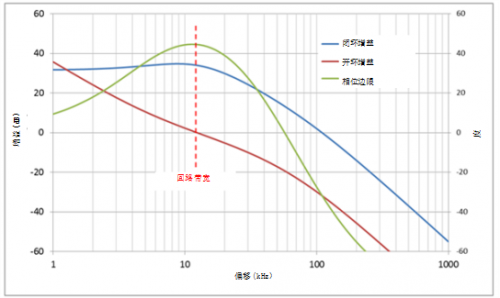

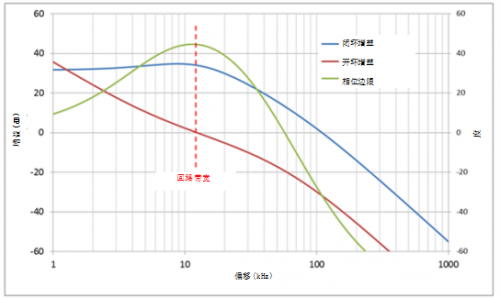

- 假設您已經通過迭代信息傳遞相位邊限和回路帶寬在鎖相環(PLL)上花費了一些時間。但遺憾地是,還是無法在相位噪聲、雜散和鎖定時間之間達成良好的平衡。感到泄氣?想要放棄?等一下!你是否試過伽馬優化參數? 伽馬優化參數 伽馬是一個數值大于零的變量。當伽馬等于1時,相位邊限在回路頻處會達到最大值(圖1)。很多回路濾波器設計方法把伽馬值設為1,這是個很好的起點,但還有進一步優化的空間。 圖1:伽馬等于1時的波德圖 伽馬能夠有效用于優化帶內相位噪聲,尤其是因壓控振蕩器 (VCO) 帶來

- 關鍵字:

PLL 回路濾波器

- 假設您已經通過迭代信息傳遞相位邊限和回路帶寬在鎖相環(PLL)上花費了一些時間。但遺憾地是,還是無法在相位噪聲、雜散和鎖定時間之間達成良好的平衡。感到泄氣?想要放棄?等一下!你是否試過伽馬優化參數? 伽馬優化參數 伽馬是一個數值大于零的變量。當伽馬等于1時,相位邊限在回路頻處會達到最大值(圖1)。很多回路濾波器設計方法把伽馬值設為1,這是個很好的起點,但還有進一步優化的空間。 圖1:伽馬等于1時的波德圖 伽馬能夠有效用于優化帶內相位噪聲,尤其是因壓控振蕩器 (VCO) 帶來

- 關鍵字:

PLL 濾波器

- 模擬鎖相環電路鎖定檢測問題解答 1.PLL鎖定有那些檢測方法,它們特點是什么? 一種是最為簡單的數字檢測,它利用輸入參考的分頻信號與VCO反饋的分頻信號,在PFD里鑒相的結果,通過連續結果時鐘周期檢測到鑒相的脈寬小于某值,作為鎖定的有效判決規則。這種檢測方式,判決方式簡單,判斷的結果只有鎖定和非鎖定兩種情況。 另一種方式是模擬鎖定檢測,也稱為N溝道漏級開路檢測,它的實現原則是通過對于PFD輸出的超前和滯后脈沖做XOR操作,直接將得出的結果輸出。由于XOR的結果有是一串高低的脈沖,所以需要外部電路

- 關鍵字:

鎖相環 PLL

- 經常有要阻擋某些頻率信號的情況,其中最常見的是50Hz或60Hz的電力線工頻。圖1中的PLL陷波濾波器可以用于阻攔不需要的頻率。IC1LM567C是一只音調解碼器。C1、R1A和R1B等元件決定了IC1探測的頻率F:F=1/[C1(R1A+R1B)]。...

- 關鍵字:

PLL 陷波濾波器

- 隨著數據轉換器的速度和分辨率不斷提升,對具有更低相位噪聲的更高頻率采樣時鐘源的需求也在不斷增長。時鐘輸入面臨的積分相位噪聲(抖動)是設計師在設計蜂窩基站、軍用雷達系統和要求高速和高性能時鐘信號的其他設計

- 關鍵字:

PLL 雙環路 相位噪聲

- 時鐘速度的提高和更嚴格的信號時序增加了對精準的高頻模塊的需求。PLL(鎖相環)基于輸入信號生成高頻輸出信號,是一種備受歡迎的用于產生高頻信號的電路。當PLL參考時鐘和PLL反饋時鐘的頻率和相位相匹配時,PLL則被稱

- 關鍵字:

PLL 時間測量

- 我們可能都見到過需要隨時間變化掃描頻率的情況。如果您遇到這樣的問題,可以考慮雷達等應用,在這類應用中發送的信號不僅可由目標反射回來,而且還能夠與接收到的信號進行比較,如下圖 1 所示。觀察頻率 (Df) 差異

- 關鍵字:

PLL 調制波形 波形調制

- 寬帶通信系統通常需要超低噪聲調節器來為VCO和PLL供電。調節器還必須能夠抑制其輸入端出現的任何紋波。在一般系統中,交流輸入轉換為隔離式直流供電軌,例如-48 V直流。該供電軌繼而轉換為隔離式12 V系統軌,為通信

- 關鍵字:

超低噪聲調節器 PLL VCO 時鐘IC 供電軌

- 十幾年前,頻率控制行業推出了基于鎖相環(PLL)的振蕩器,這是一項開拓性創新技術,采用了傳統晶體振蕩器(XO)所沒有的多項特性。憑借內部時鐘合成器IC技術,基于PLL的XO可編程來支持更寬廣的頻率范圍。這一突破消除了

- 關鍵字:

鎖相環 PLL 振蕩器 抖動 相位噪聲

- 對鎖相環環路濾波器進行簡單分析,對ADIsimPLL 3.1模擬軟件的功能特點做了簡要介紹,并利用仿真軟件對一款頻率合成器的環路濾波器進行仿真設計,結果表明該軟件在設計應用中方便快捷,能夠幫助設計出滿足指標要求且性能穩定的環路濾波器。

- 關鍵字:

環路帶寬 PLL 環路濾波器 壓控靈敏度

pll-based介紹

您好,目前還沒有人創建詞條pll-based!

歡迎您創建該詞條,闡述對pll-based的理解,并與今后在此搜索pll-based的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473