1 引言

隨著現代通信技術的不斷發展,對頻率源的要求越來越高。一方面,由于通信容量的迅速擴大,使得通信頻譜不斷向高端擴展;另一方面,由于頻譜資源的相對匱乏,必須提高頻譜利用率,進而對頻率源的頻譜純度和頻率穩定度都提出了更高的要求。

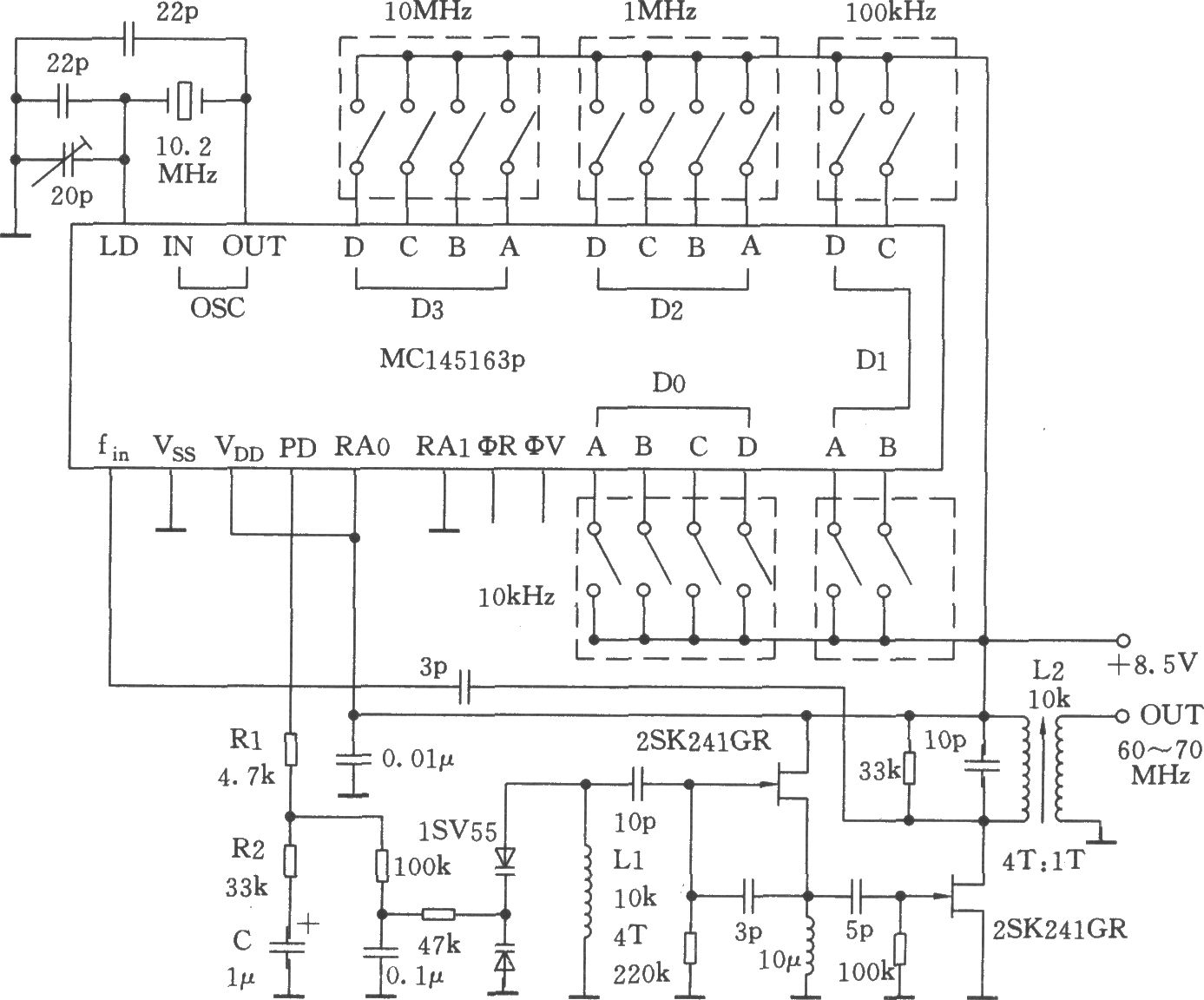

在無線通信領域中,為了提高頻譜利用率,現代通信系統對頻率合成器的精度、頻率分辨率、轉換時間和頻譜純度等指標提出了越來越高的要求。頻率合成的方法主要有直接頻率合成(DS)、間接頻率合成(PLL)和直接數字頻率合成(DDS)等方案。直接頻率合成體積大、成本高, 有較

關鍵字:

X波段 PLL VCO

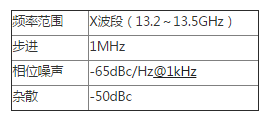

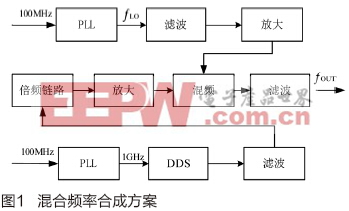

摘要:本文介紹了一種C波段寬帶捷變頻率綜合器的設計方法,采用直接數字頻率合成器(DDS)實現頻率捷變,采用倍頻鏈路擴展輸出帶寬,通過與鎖相環(PLL)合成產生的本振信號混頻將輸出頻率搬移到C波段。論述了DDS時鐘電路、倍頻鏈路以及混頻部分的設計方法,并給出了達到的主要技術指標和測試結果。

引言

頻率合成器是現代通訊系統必不可少的關鍵電路, 是電子系統的主要信號源,是決定電子系統性能的關鍵設備。隨著系統對頻率源的頻率穩定度、頻譜純度、頻率范圍和輸出頻率個數的要求越來越高,高穩定、低相位噪聲、

關鍵字:

變頻率綜合器 DDS PLL C波段 合成器 201410

1、前言

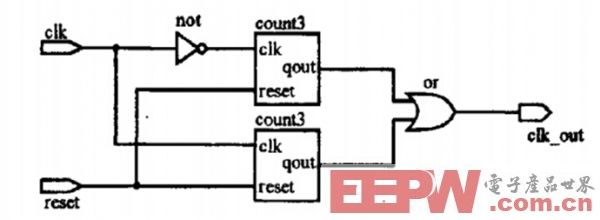

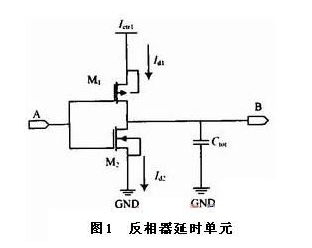

分頻器是FPGA設計中使用頻率非常高的基本單元之一。盡管目前在大部分設計中還廣泛使用集成鎖相環(如Altera的PLL,Xilinx的DLL)來進行時鐘的分頻、倍頻以及相移設計,但是,對于時鐘要求不太嚴格的設計,通過自主設計進行時鐘分頻的實現方法仍然非常流行。首先這種方法可以節省鎖相環資源,再者這種方式只消耗不多的邏輯單元就可以達到對時鐘的操作目的。

2、整數倍分頻器的設計

2.1 偶數倍分頻

偶數倍分頻器的實現非常簡單,只需要一個計數器進行計數就能實現。如需要N分頻

關鍵字:

FPGA 分頻器 PLL

電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

關鍵字:

定時應用 PLL 振蕩器 內部時鐘 合成器IC技術

高性能模擬與混合信號IC領導廠商Silicon Labs(芯科實驗室有限公司)今日宣布針對高速網絡、通信和數據中心等當今互聯網基礎設施的根基,推出業界最高頻率靈活性和領先抖動性能的時鐘解決方案。Silicon Labs的新一代Si534x“片上時鐘樹“系列產品包括高性能時鐘發生器和高集成度Multi-PLL抖動衰減器。這些單芯片、超低抖動時鐘芯片整合了時鐘合成與抖動衰減功能,設計旨在減少光傳輸網絡、無線基礎設施、寬帶接入/匯聚、電信級以太網、測試和測量以及企業和數據中心設備(包

關鍵字:

Silicon Labs Multi-PLL 時鐘

十幾年前,頻率控制行業推出了基于鎖相環(PLL)的振蕩器,這是一項開拓性創新技術,采用了傳統晶體振蕩器(XO)所沒有的多項特性。憑借內部時鐘合成器IC技術,基于PLL的XO可編程來支持更寬廣的頻率范圍。這一突破消除了為在特定頻率實現共振而切割和加工石英所需的材料加工工藝步驟。這一創新也使得對基于PLL的XO進行頻率編程成為可能并且實現極短交貨周期。

鑒于傳統振蕩器交貨周期可能接近14周或更長,許多硬件設計人員渴望利用可編程振蕩器獲得顯著的交貨周期優勢。不幸的是,嚴重的問題發生了。一些已經從傳統X

關鍵字:

振蕩器 PLL SoC

高性能模擬與混合信號IC領導廠商Silicon Labs今日宣布針對高速網絡、通信和數據中心等當今互聯網基礎設施的根基,推出業界最高頻率靈活性和領先抖動性能的時鐘解決方案。Silicon Labs的新一代Si534x“片上時鐘樹“系列產品包括高性能時鐘發生器和高集成度Multi-PLL抖動衰減器。這些單芯片、超低抖動時鐘芯片整合了時鐘合成與抖動衰減功能,設計旨在減少光傳輸網絡、無線基礎設施、寬帶接入/匯聚、電信級以太網、測試和測量以及企業和數據中心設備(包括邊緣路由器、交換機、

關鍵字:

Silicon Labs Si534x Multi-PLL

Analog Devices, Inc.(ADI),全球領先的高性能信號處理解決方案提供商,最近推出了ADIsimPE?(個人版)仿真器,此款仿真器適合線性和混合信號應用,能夠進行虛擬原型開發,以滿足資源有限且要求產品快速上市的客戶的需求。ADIsimPE由SIMetrix/SIMPLIS?仿真器供電,它使用SIMetrix SPICE仿真線性電路,如精密基準電壓源、運算放大器和線性調節器以及SIMPLIS(分段線性系統仿真),從而高速分析PLL之類的非線性電路并且能夠切換電源

關鍵字:

Analog Devices ADIsimPower PLL

日前,德州儀器 (TI) 宣布推出支持高級頻率調制功能的業界最高性能 14GHz 分數 N分頻PLLatinum? 鎖相環 (PLL)。該 LMX2492 提供業界最佳噪聲性能,比性能最接近的同類競爭器件低 6dB,可提升射頻 (RF) 靈敏度以及雷達覆蓋范圍及精確度。此外,該器件還支持 200MHz 的相位頻率檢測器、5V 充電泵電源以及 500 MHz 至 14GHz 的寬泛工作頻率。LMX2492 提供工業及汽車級(1 級)版本,適用于軍事與汽車雷達、微波回程、通信以及測量測試應用。 LMX2

關鍵字:

TI PLL LMX2492

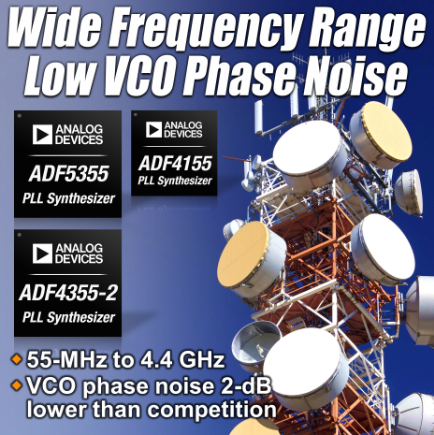

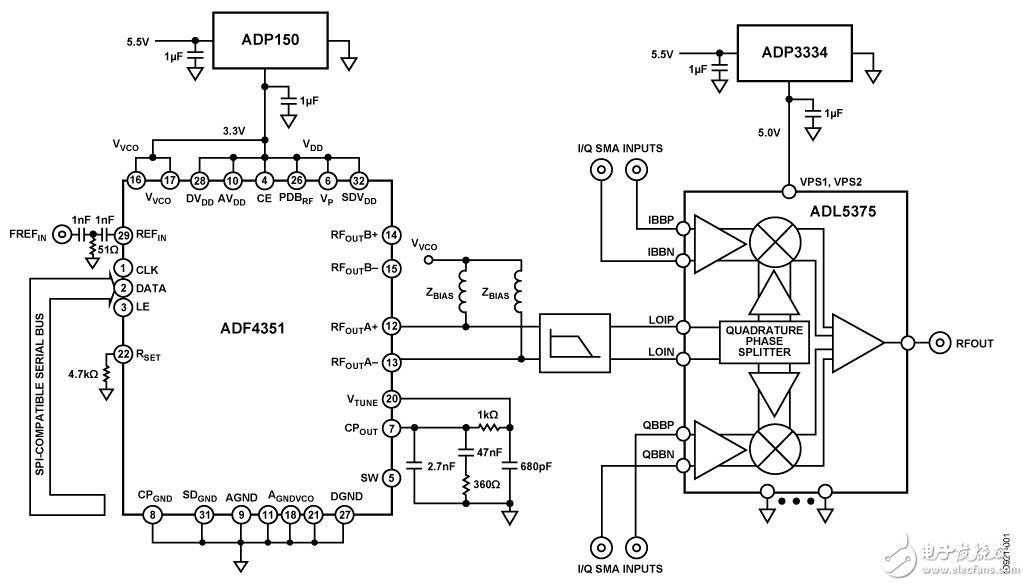

Analog Devices, Inc. (NASDAQ:ADI)近日發布三款全新的鎖相環(PLL)器件ADF5355/ADF4355-2/ADF4155,其中一款具有業界最寬的頻率覆蓋范圍和最低的壓控振蕩器(VCO)相位噪聲,且在單個器件中實現這些性能。ADF5355 PLL具有同類最寬的55 MHz至14 GHz頻譜范圍;而ADF4355-2 PLL的頻譜范圍為55 MHz至4.4 GHz。這些器件可供需要單片高性能寬帶頻率合成器的RF和微波通信系統設計人員使用。這兩款PLL均集成超低相位噪聲VC

關鍵字:

ADI PLL ADF5355

相位噪聲源:

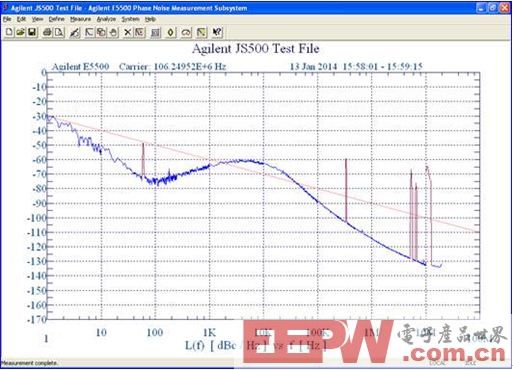

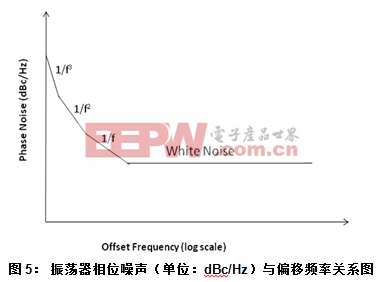

振蕩器的單邊帶相位噪聲主要特性通常如圖5所示,該相位噪聲(單位:dBc/Hz)在對數尺度上被繪制成偏移頻率f0的函數。

實際曲線近似由一系列區間構成,每一區間的斜率為1/fx,其中X=0表示白相位噪聲區間,即此時曲線斜率為0dB/decade。當X=1時,相位噪聲區間則稱為閃爍相位噪聲,其斜率為-20dB/decade。依此類推,其它區間則對應更大的X值。X值越大的區間與載波頻率越接近。

圖6所示為PLL時鐘發生器中相位噪聲的曲線圖。需要注意的是,本圖與前述圖5中所示的

關鍵字:

IC時鐘 PLL 噪聲 振蕩器 相位抖動

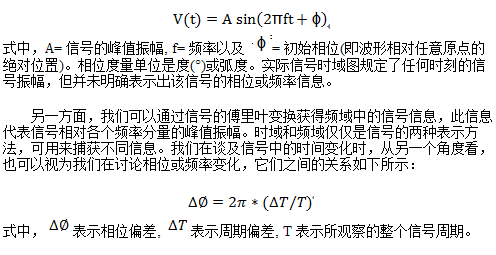

我們在本系列文章的前一部分[鏈接]已經討論了鎖相環(PLL)的應用以及在時鐘分配系統中,PLL相對于傳統振蕩器的優勢。接下來我們將會闡述基于PLL的時鐘分配系統的重要參數,這些參數都是設計時必須考慮的。例如,在實踐過程中,時鐘的準確時序對所有分配系統而言都非常重要。如果時鐘位置偏差范圍大,則可能會導致系統發生故障。時域中的這些偏差被稱為“抖動”。此外,抖動又分多個類別,譬如周期性抖動、周期間抖動、RMS抖動、長期抖動以及相位抖動。在本章節,我們將重點闡述“相位抖動&

關鍵字:

IC時鐘 PLL 噪聲 振蕩器 相位抖動

頻率源作為電子系統的核心,是決定電子系統性能的關鍵設備。雷達、通信、電子偵察和對抗設備中,高性能的頻率源是實現其整體設備高性能指標的關鍵技術之一。頻率源的相位噪聲和雜散抑制的性能直接影響整個系統的性能。其中采用鎖相環設計的頻率源具有輸出頻率高、頻率穩定度高、頻率純、低相噪、雜散抑制好等優點。

關鍵字:

PLL VCO AVR

一個采用典型無源環路濾波器的PLL系統如圖5所示,其中包括以I_Leakage表示的電流源,代表充電泵的泄漏電流。假定PLL是鎖定的,那么I_Leakage在充電泵關斷時,減少了CP保持的電量。當充電泵每PFD周期接通一次時,ICP_UP通過加上一個短的電流脈沖,補充CP損失的電量。

關鍵字:

PLL VCO IC

本文給出了一種簡單的模型,可用來在PLL系統中準確地預測由于充電泵和/或運算放大器泄漏電流引起的基準雜散噪聲的大小。知道如何預測這類噪聲有助于在PLL系統設計的早期明智地選擇環路參數。

關鍵字:

PLL VCO IC

pll-based介紹

您好,目前還沒有人創建詞條pll-based!

歡迎您創建該詞條,闡述對pll-based的理解,并與今后在此搜索pll-based的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473