pll-based 文章 最新資訊

TLi選擇FineSim SPICE作為模擬IC設(shè)計(jì)的標(biāo)準(zhǔn)驗(yàn)證工具

- 芯片設(shè)計(jì)解決方案供應(yīng)商微捷碼(Magma®)設(shè)計(jì)自動(dòng)化有限公司日前宣布,消費(fèi)電子產(chǎn)品全球供應(yīng)商Technology Leaders & Innovators (TLi)公司已采用FineSim™ SPICE作為大型模擬IP設(shè)計(jì)的標(biāo)準(zhǔn)驗(yàn)證工具。TLi是在對大量商用SPICE仿真產(chǎn)品進(jìn)行徹底詳盡的評估,結(jié)果顯示具有線性多CPU功能的FineSim SPICE提供了較傳統(tǒng)多線程仿真器快上一個(gè)數(shù)量級(jí)的運(yùn)行時(shí)間后才決定選用這款微捷碼軟件。 “我們設(shè)計(jì)著許多不同類型的

- 關(guān)鍵字: Magma FineSim PLL ADC/DAC 高速I/O

一種基于DDS和PLL技術(shù)本振源的設(shè)計(jì)與實(shí)現(xiàn)

- 現(xiàn)代頻率合成技術(shù)正朝著高性能、小型化的方向發(fā)展,應(yīng)用最為廣泛的是直接數(shù)字式頻率合成器(DDS)和鎖相式頻率合成器(PLL)。介紹直接數(shù)字頻率合成器和鎖相環(huán)頻率合成器的基本原理,簡述用直接數(shù)字頻率合成器(AD9954)和鎖相環(huán)頻率合成器(ADF4112)所設(shè)計(jì)的本振源的實(shí)現(xiàn)方案,重點(diǎn)闡述了系統(tǒng)的硬件實(shí)現(xiàn),包括系統(tǒng)原理、主要電路單元設(shè)計(jì)等,并且對系統(tǒng)的相位噪聲和雜散性能做了簡要分析,最后給出了系統(tǒng)測試結(jié)果。

- 關(guān)鍵字: DDS PLL

IDT 推出 Versacloc 計(jì)時(shí)器件新產(chǎn)品系列

- 致力于豐富數(shù)字媒體體驗(yàn)、提供領(lǐng)先的混合信號(hào)半導(dǎo)體解決方案供應(yīng)商 IDT® 公司(Integrated Device Technology, Inc.)推出其 VersaClock™ 計(jì)時(shí)器件的最新產(chǎn)品系列。VersaClock III 器件是專為高性能消費(fèi)、電信、網(wǎng)絡(luò)和數(shù)據(jù)通信應(yīng)用設(shè)計(jì)的可編程時(shí)鐘發(fā)生器,可以更經(jīng)濟(jì)有效地在多個(gè)晶體和振蕩器之間進(jìn)行選擇。這些可編程計(jì)時(shí)解決方案對節(jié)省占板空間和保持功效非常關(guān)鍵,因其體積可能不允許全定制解決方案。多個(gè)具有各種不同需求的系統(tǒng)能夠整合成更少的

- 關(guān)鍵字: IDT VersaClock 可編程時(shí)鐘發(fā)生器 PLL

MIPS授權(quán)中科院計(jì)算技術(shù)研究所使用MIPS架構(gòu)

- MIPS 科技公司宣布,中國科學(xué)院計(jì)算技術(shù)研究所已獲得 MIPS32 和 MIPS64 架構(gòu)授權(quán),以進(jìn)一步推動(dòng)龍芯系列處理器的開發(fā)與商業(yè)化工作。在 2007 年,MIPS 科技的授權(quán)客戶意法半導(dǎo)體(STMicroelectronics)選用 MIPS64 架構(gòu)來支持 ICT 的龍芯處理器研發(fā)。本次則是該機(jī)構(gòu)首度直接取得 MIPS 架構(gòu)授權(quán)。 中國科學(xué)院計(jì)算技術(shù)研究所(ICT)所長李國杰先生表示:“我們非常高興能與 MIPS 強(qiáng)化合作關(guān)系,以持續(xù)推動(dòng)新技術(shù)在中國的創(chuàng)新與采用。業(yè)界標(biāo)準(zhǔn)

- 關(guān)鍵字: MIPS 龍芯 MIPS32 MIPS64 MIPS-based

MIPS科技宣布推出在MIPS架構(gòu)上的Android平臺(tái)

- 為家庭娛樂、通信、網(wǎng)絡(luò)和便攜多媒體市場提供業(yè)界標(biāo)準(zhǔn)處理器架構(gòu)和內(nèi)核的領(lǐng)導(dǎo)廠商 MIPS 科技公司(MIPS Technologies, Inc)今天宣布,推出其行業(yè)標(biāo)準(zhǔn) MIPS 架構(gòu)的 Android™ 平臺(tái)。MIPS 科技還宣布將在 60 天內(nèi)公開MIPS優(yōu)化后的源代碼。這一舉措由若干生態(tài)系統(tǒng)合作伙伴共同推動(dòng),未來還會(huì)有更多合作伙伴加入,將 Android 帶給全球廣大的 MIPS 開發(fā)社區(qū),現(xiàn)在就可以開始采用這一革命性的平臺(tái)進(jìn)行數(shù)字電視、移動(dòng)互聯(lián)網(wǎng)設(shè)備(MID)、數(shù)碼相框(DPF)和

- 關(guān)鍵字: MIPS 數(shù)字電視 Android MIPS-Based

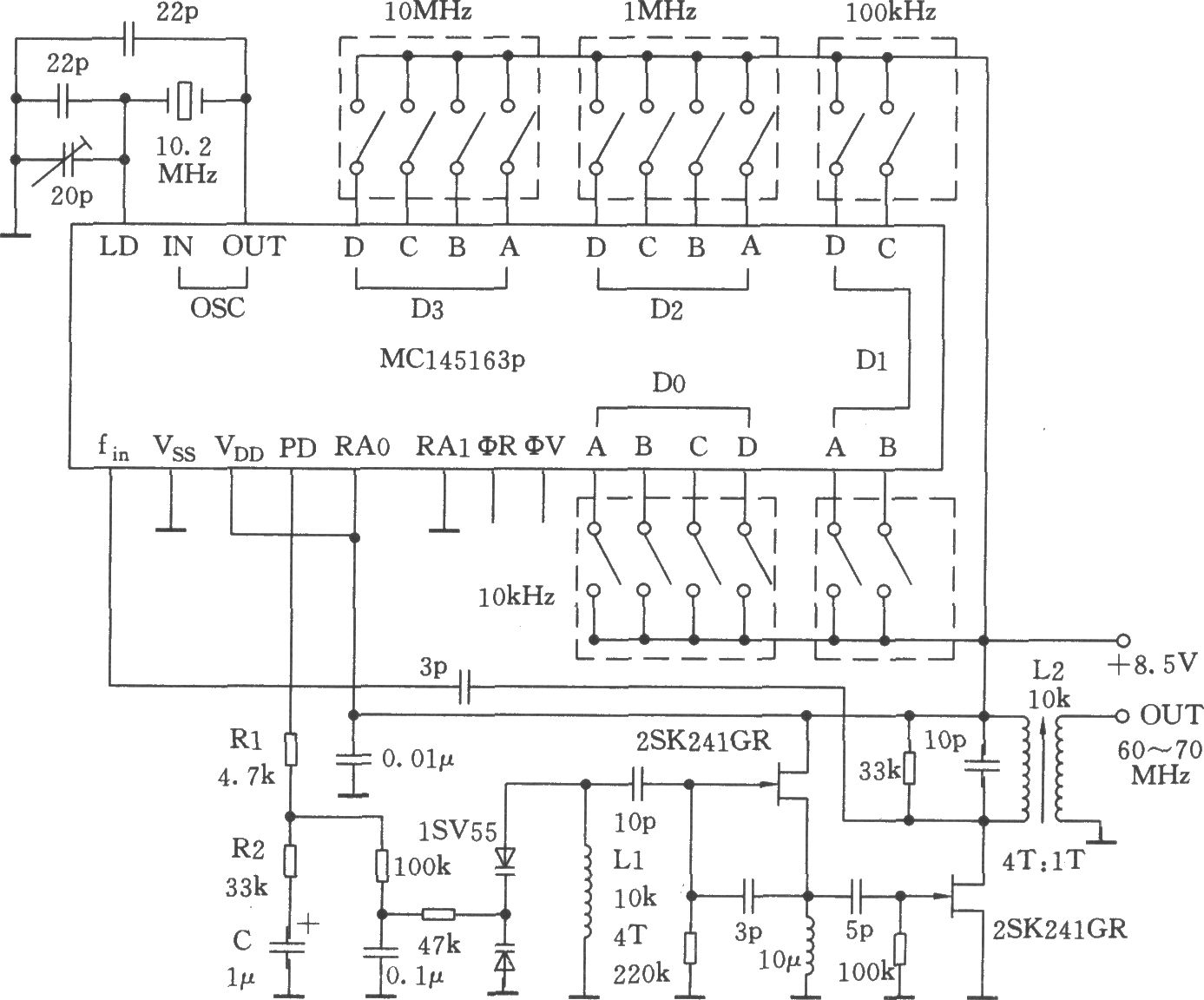

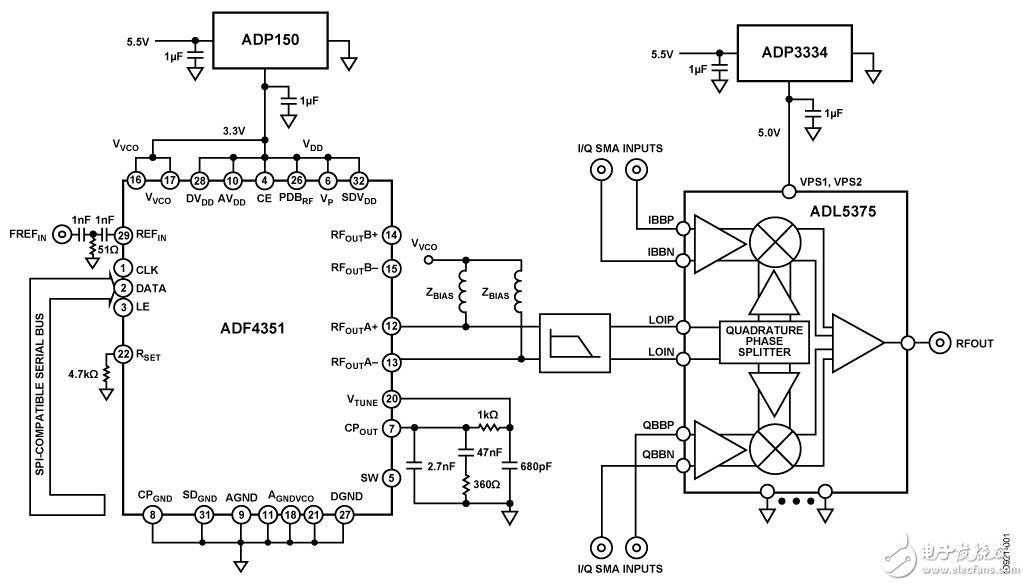

基于DDS驅(qū)動(dòng)PLL結(jié)構(gòu)的寬帶頻率合成器設(shè)計(jì)

- 摘 要:結(jié)合數(shù)字式頻率合成器(DDs)和集成鎖相環(huán)(PLL)各自的優(yōu)點(diǎn),研制并設(shè)計(jì)了以DDS芯片AD9954和集成鎖相芯片ADF4113構(gòu)成的高分辨率、低雜散、寬頻段頻率合成器,并對該頻率合成器進(jìn)行了分析和仿真,從仿真和測試結(jié)果

- 關(guān)鍵字: DDS PLL 驅(qū)動(dòng) 寬帶頻率

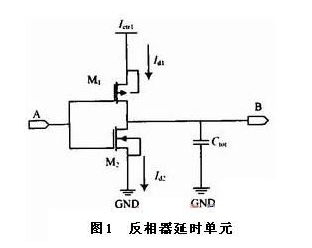

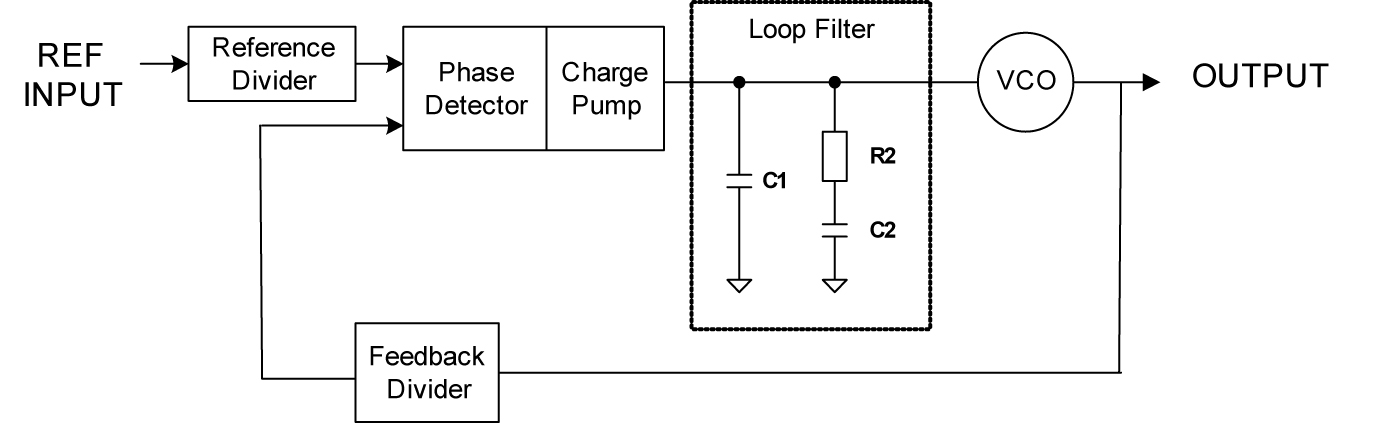

基于DDS的數(shù)字PLL

- 多年以來,作為業(yè)界主流產(chǎn)品的模擬PLL已被熟知,模擬PLL性能穩(wěn)定,可為頻率合成和抖動(dòng)消除提供低成本的解決方案,工作頻率高達(dá)8GHz及以上。然而新興的基于直接數(shù)字頻率合成(DDS)的數(shù)字PLL在某些應(yīng)用中極具競爭力。本文比較了模擬PLL和基于DDS的數(shù)字PLL之間的差異,以及如何利用這些差異來指導(dǎo)設(shè)計(jì)人員選擇最佳的解決方案。 數(shù)字PLL利用數(shù)字邏輯實(shí)現(xiàn)傳統(tǒng)的PLL模塊。雖然實(shí)現(xiàn)數(shù)字PLL的方法有很多,但本文只介紹基于DDS的數(shù)字PLL架構(gòu)。 圖1 典型的模擬PLL結(jié)構(gòu)框圖

- 關(guān)鍵字: PLL DDS 分頻器 鑒相器 DAC VCO

基于多個(gè)特征分塊貝葉斯分類器融合策略的人臉識(shí)別方法

- 摘要:提出一種基于奇異值分解和貝葉斯決策的人臉特征提取與識(shí)別算法。通過對人臉圖像樣本進(jìn)行幾何歸一化和灰度均衡化后,結(jié)合分塊與加權(quán),運(yùn)用奇異值分解,分別獲得特征臉和標(biāo)準(zhǔn)臉,然后采用多個(gè)基于特征分塊的貝葉斯分類器(FBBC)的融合策略進(jìn)行分類識(shí)別。實(shí)驗(yàn)驗(yàn)證了該方法的有效性,具有良好的精煉和實(shí)時(shí)性品質(zhì)指標(biāo)。 關(guān)鍵詞:奇異值分解;貝葉斯決策;人臉特征;分類;圖像 引言 人臉識(shí)別是指利用計(jì)算機(jī)對人臉圖像進(jìn)行分析,從中提取有效的識(shí)別信息,用來鑒別身份的一種技術(shù),具有直接、友好、方便等優(yōu)點(diǎn)。基于奇異值特征的人

- 關(guān)鍵字: A Method of Face Recognition Based on the Fusion of Multiple Feature Block Bayesian Classifiers 200810

ADI公司的可編程時(shí)鐘發(fā)生器簡化系統(tǒng)設(shè)計(jì)并減少時(shí)鐘器件數(shù)量

- 中國 北京——Analog Devices, Inc.(紐約證券交易所代碼:ADI),全球領(lǐng)先的高性能信號(hào)處理解決方案供應(yīng)商,最新推出一對時(shí)鐘發(fā)生與分配IC——AD9520與AD9522,實(shí)現(xiàn)了業(yè)界最佳的器件集成度、低噪聲、低抖動(dòng)性能與信號(hào)輸出靈活性的完美組合。 AD9520與AD9522多輸出時(shí)鐘發(fā)生器內(nèi)置一個(gè)512 Byte的嵌入式EEPROM存儲(chǔ)器模塊,為系統(tǒng)工程師提供了可用作時(shí)鐘源和系統(tǒng)時(shí)鐘的雙重可編程時(shí)鐘解決方案。通過利用片上存儲(chǔ)器對具體的輸出

- 關(guān)鍵字: EEPROM 冗余基準(zhǔn) PLL Analog Devices

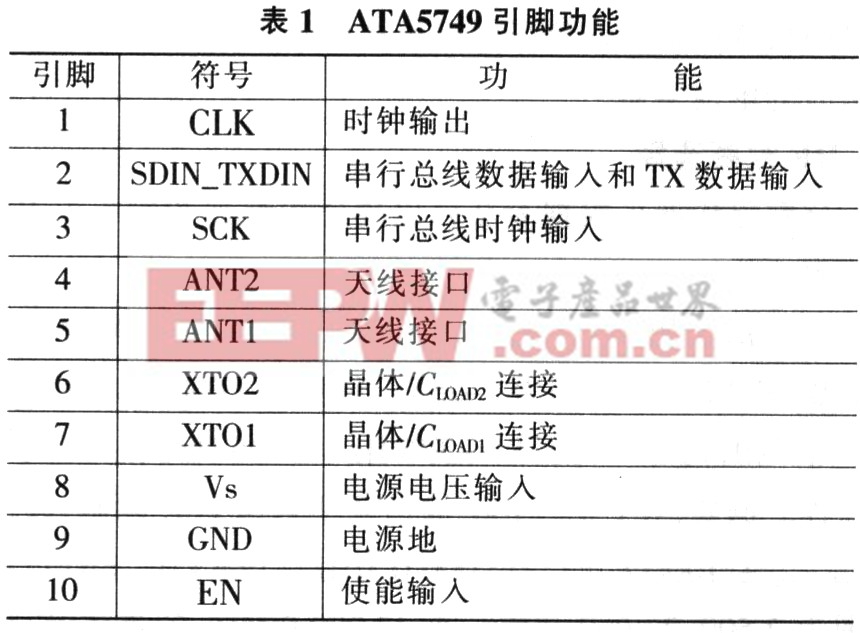

Maxim推出基于晶體的鎖相環(huán)300MHz至450MHz ASK/FSK發(fā)送器

- Maxim推出基于晶體的鎖相環(huán)(PLL) VHF/UHF發(fā)送器MAX7057,能夠在較寬的頻率范圍內(nèi)發(fā)送OOK/ASK/FSK數(shù)據(jù)。器件配合適當(dāng)?shù)木w頻率,可以發(fā)送300MHz至450MHz范圍內(nèi)的任何信號(hào),并能夠以高達(dá)100kbps的速率發(fā)送NRZ碼(50kbps曼徹斯特碼)。 MAX7057集成了可編程分?jǐn)?shù)N PLL合成器和寬帶VCO,因而具有極大的靈活性。此外,還可以設(shè)置內(nèi)部電容,實(shí)現(xiàn)功率放大器(PA)與天線之間的阻抗匹配。這種拓?fù)浣Y(jié)構(gòu)可確保多個(gè)工作頻率下的高效率傳輸,從而使MAX7057

- 關(guān)鍵字: Maxim PLL 鎖相環(huán) 發(fā)送器

TI推出1.8V 可編程 VCXO 3-PLL 時(shí)鐘合成器

- CDCE937 和 CDCEL937 均為基于 PLL 模塊的、低成本、高性能的可編程時(shí)鐘合成器,可以在單輸入頻率的不同頻率下生成多達(dá)七個(gè)輸出時(shí)鐘。每一個(gè)輸出均可以進(jìn)行系統(tǒng)內(nèi)編程,從而使用三個(gè)獨(dú)立的可配置 PLL 就可用于任何高達(dá) 230MHz 的時(shí)鐘頻率。該器件具有簡單的頻率同步,使零-PPM 時(shí)鐘生成成為可能。另外,這兩種合成器還具有擴(kuò)頻時(shí)鐘及片上 EEPROM 和通過 SDA/SCL 進(jìn)行系統(tǒng)內(nèi)熱編程的特點(diǎn)。對于數(shù)字媒體系統(tǒng)、流媒體、GPS 接收機(jī)、便攜式媒體以及DSP/OMAP/DaVinci

- 關(guān)鍵字: TI 時(shí)鐘合成器 可編程 PLL

基于多路移相時(shí)鐘的瞬時(shí)測頻模塊設(shè)計(jì)

- 0 引 言 目前,脈沖雷達(dá)的脈內(nèi)信號(hào)分析一直是研究的熱點(diǎn)和難點(diǎn),如何能更快速,準(zhǔn)確的對脈內(nèi)載波頻率測量成為研究人員關(guān)注的目標(biāo),與此同時(shí)高精度頻率源在無線電領(lǐng)域應(yīng)用越來越廣泛,對頻率測量設(shè)備有了更高的要求,因此研究新的測頻方法對開發(fā)低成本、小體積且使用和攜帶方便的頻率測量設(shè)備有著十分重要的意義。本文根據(jù)雷達(dá)發(fā)射機(jī)頻率快速變化的特點(diǎn),采用目前新型的邏輯控制器件研究新型頻率測量模塊,結(jié)合等精度內(nèi)插測頻原理,對整形放大后的脈沖直接計(jì)數(shù),實(shí)現(xiàn)對下變頻后單脈沖包絡(luò)的載波快速測頻。具有測量精度高,測量用時(shí)短的

- 關(guān)鍵字: 測頻模塊 時(shí)鐘內(nèi)插 時(shí)鐘移相 PLL 脈內(nèi)測頻

特瑞仕推出超小型PLL時(shí)鐘發(fā)生器

- 特瑞仕半導(dǎo)體株式會(huì)社開發(fā)了XC25BS8系列內(nèi)置分頻、倍頻電路超小型PLL時(shí)鐘發(fā)生器。 XC25BS8系列是能在低頻輸入8kHz、4095倍的范圍內(nèi)倍頻工作的PLL時(shí)鐘發(fā)生器IC。 輸入端分頻因子(M)可從1~2047的分頻范圍內(nèi)進(jìn)行選擇;輸出端分頻因子(N)可從1~4095的分頻范圍內(nèi)進(jìn)行選擇。輸出頻率在1MHz~100MHz的范圍內(nèi),輸入時(shí)鐘為8kHz~36MHz的標(biāo)準(zhǔn)時(shí)鐘。在內(nèi)部可進(jìn)行微調(diào),在少量外置部件的條件下動(dòng)作。從CE端子輸入低電平信號(hào),可停止整個(gè)芯片動(dòng)作,抑制

- 關(guān)鍵字: 半導(dǎo)體 特瑞仕 時(shí)鐘發(fā)生器 PLL

pll-based介紹

您好,目前還沒有人創(chuàng)建詞條pll-based!

歡迎您創(chuàng)建該詞條,闡述對pll-based的理解,并與今后在此搜索pll-based的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對pll-based的理解,并與今后在此搜索pll-based的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司