fsp:fpga-pcb 文章 最新資訊

非隔離式開關(guān)電源的PCB布局全攻略

- 1.引言 一個良好的布局設(shè)計(jì)可優(yōu)化效率,減緩熱應(yīng)力并盡量小走線與元件之間噪聲作用。這切都 源于設(shè)計(jì)人員對電中流傳導(dǎo)路徑以及信號的理解。 當(dāng)一塊原型電源板首次加時,最好的情況 是它不僅能工作而且還安靜、發(fā)熱低。然這種并不多見。 開關(guān)電源的一個常見問題是 “不穩(wěn)定 ”的開關(guān)波形。有些時候,抖動處于聲段磁性元件會產(chǎn)生 出音頻噪聲。如果問題在印刷電路板的布局上, 要找原因可能會很困難此開關(guān)電源 設(shè)計(jì)初期的 正確 P

- 關(guān)鍵字: 開關(guān)電源 PCB

聊一聊PCB規(guī)劃、布局和布線方面的設(shè)計(jì)技巧

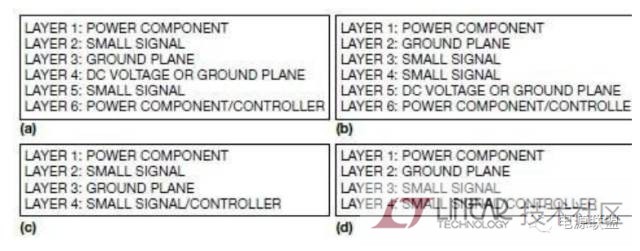

- 在開始布線之前應(yīng)該對設(shè)計(jì)進(jìn)行認(rèn)真的分析以及對工具軟件進(jìn)行認(rèn)真的設(shè)置,這會使設(shè)計(jì)更加符合要求。 1 確定PCB的層數(shù) 電路板尺寸和布線層數(shù)需要在設(shè)計(jì)初期確定。布線層的數(shù)量以及層疊(STack-up)方式會直接影響到印制線的布線和阻抗。板的大小有助于確定層疊方式和印制線寬度,實(shí)現(xiàn)期望的設(shè)計(jì)效果。目前多層板之間的成本差別很小,在開始設(shè)計(jì)時最好采用較多的電路層并使敷銅均勻分布。 2 設(shè)計(jì)規(guī)則和限制 要順利完成布線任務(wù),布線工具需要在正確的規(guī)則和限制條件下工作。要對所有特殊要求的信號

- 關(guān)鍵字: PCB

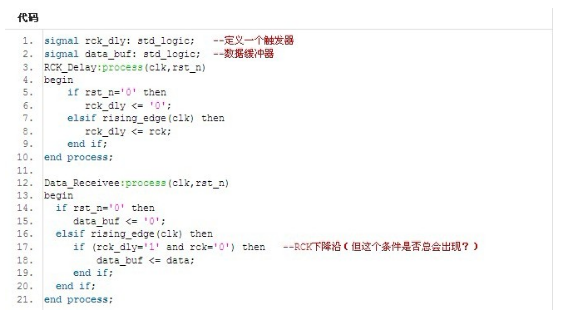

FPGA設(shè)計(jì)經(jīng)驗(yàn)之邊沿檢測

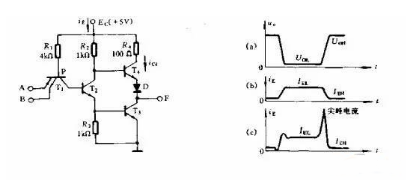

- 在同步電路設(shè)計(jì)中,邊沿檢測是必不可少的! 例如:在一個時鐘頻率16MHz的同步串行總線接收電路里,串行總線波特率為1Mbps。在串行總線的發(fā)送端是在同步時鐘(1MHz)的上升沿輸出數(shù)據(jù),在接收端在同步時鐘的下降沿對輸入數(shù)據(jù)進(jìn)行接收采樣。在這個接收電路里檢測同步時鐘的下降沿是必不可少的。假設(shè)主時鐘-clk,同步時鐘-rck,同步數(shù)據(jù)-data。 有些人在邊沿檢測的時候就喜歡這樣做: 但是大家忽略了一種情況,就是clk與rck之間比沒有必然的同步關(guān)系,當(dāng)r

- 關(guān)鍵字: FPGA 邊沿檢測

硬件工程師談高速PCB信號走線規(guī)則TOP9

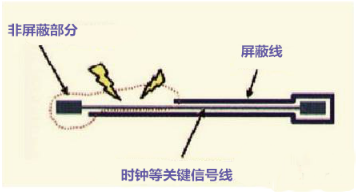

- 規(guī)則一:高速信號走線屏蔽規(guī)則 在高速的PCB設(shè)計(jì)中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。 圖1 高速信號線 規(guī)則二:高速信號的走線閉環(huán)規(guī)則 由于PCB板的密度越來越高,很多PCB LAYOUT工程師在走線的過程中,很容易出現(xiàn)一種失誤,即時鐘信號等高速信號網(wǎng)絡(luò),在多層的PCB走線的時候產(chǎn)生了閉環(huán)的結(jié)果,這樣的閉環(huán)結(jié)果將產(chǎn)生環(huán)形天線,增加EMI的輻射強(qiáng)度。 圖2 閉環(huán)

- 關(guān)鍵字: PCB 硬件工程師

EDA技術(shù)在電路設(shè)計(jì)中的地位和作用

- 20世紀(jì)后半期,隨著集成電路和計(jì)算機(jī)技術(shù)的發(fā)展,數(shù)字系統(tǒng)也得到了飛速發(fā)展,其實(shí)現(xiàn)方法經(jīng)歷了由分立元件、SSI、MSI到LSI、VLSI以及UVLSI的過程。同時為了提高系統(tǒng)的可靠性與通用性,微處理器和專用集成電路(ASIC)逐漸取代了通用集成硬件LSI電路,而在這兩者之間,ASIC以其體積小、重量輕、功耗低、速度快、成本低、保密性好而脫穎而出。總的來說,ASIC的制作可粗略地分為掩膜式方法和現(xiàn)場可編程方法兩大類。目前,業(yè)界大量可編程器件(PLD),尤其是現(xiàn)場可編程邏輯器件(CPLD/FPGA)被大量地

- 關(guān)鍵字: EDA PCB

Achronix開設(shè)上海代表處以支持大中華地區(qū)對其FPGA產(chǎn)品的強(qiáng)勁需求

- Achronix今日宣布其已在上海開設(shè)新的辦公室,以組建由工程與技術(shù)支持專業(yè)人員組成的本地團(tuán)隊(duì)。新辦公室的這支團(tuán)隊(duì)將與Achronix在全球其他地點(diǎn)的團(tuán)隊(duì)密切合作,為大中華地區(qū)的客戶提供支持。該辦公室位于上海張江高科技園區(qū)長泰廣場,所在區(qū)域?yàn)槲覈呻娐樊a(chǎn)業(yè)中心之一。 Achronix在2017年的營業(yè)收入將比上年增長700%,使其成為2017年成長最快的半導(dǎo)體公司之一;其快速增長的營業(yè)收入得益于客戶對最高性能、低功耗、可編程的基于FPGA的硬件加速解決方案的強(qiáng)勁需求。這些需求來自于諸如軟件定義網(wǎng)絡(luò)

- 關(guān)鍵字: Achronix FPGA

基于Verilog語言的等精度頻率計(jì)設(shè)計(jì)

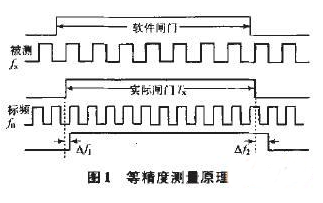

- 引言 傳統(tǒng)測量頻率的方法主要有直接測量法、分頻測量法、測周法等,這些方法往往只適用于測量一段頻率,當(dāng)被測信號的頻率發(fā)生變化時,測量的精度就會下降。本文提出一種基于等精度原理的測量頻率的方法,在整個頻率測量過程中都能達(dá)到相同的測量精度,而與被測信號的頻率變化無關(guān)。本文利用FPGA(現(xiàn)場可編程門陣列)的高速數(shù)據(jù)處理能力,實(shí)現(xiàn)對被測信號的測量計(jì)數(shù);利用單片機(jī)的運(yùn)算和控制能力,實(shí)現(xiàn)對頻率、周期、脈沖寬度的計(jì)算及顯示。 等精度測量原理等精度測量的一個最大特點(diǎn)是測量的實(shí)際門控時間不是一個固定值,而

- 關(guān)鍵字: Verilog FPGA

基于FPGA自適應(yīng)數(shù)字頻率計(jì)的設(shè)計(jì)

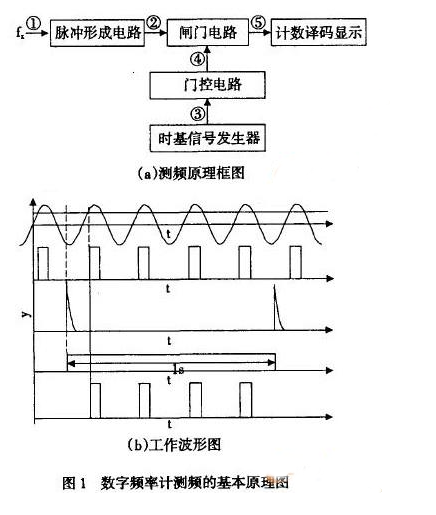

- 在電子工程,資源勘探,儀器儀表等相關(guān)應(yīng)用中,頻率計(jì)是工程技術(shù)人員必不可少的測量工具。頻率測量也是電子測量技術(shù)中最基本最常見的測量之一。不少物理量的測量,如轉(zhuǎn)速、振動頻率等的測量都涉及到或可以轉(zhuǎn)化為頻率的測量。目前,市場上有各種多功能、高精度、高頻率的數(shù)字頻率計(jì),但價(jià)格不菲。為適應(yīng)實(shí)際工作的需要,本文在簡述頻率測量的基本原理和方法的基礎(chǔ)上,提供一種基于FPGA的數(shù)字頻率計(jì)的設(shè)計(jì)和實(shí)現(xiàn)過程,本方案不但切實(shí)可行,而且具有成本低廉、小巧輕便、便于攜帶等特點(diǎn)。 1 數(shù)字頻率測量原理和方法及本系統(tǒng)硬件

- 關(guān)鍵字: FPGA 數(shù)字頻率計(jì)

基于Verilog FPGA 流水燈設(shè)計(jì)

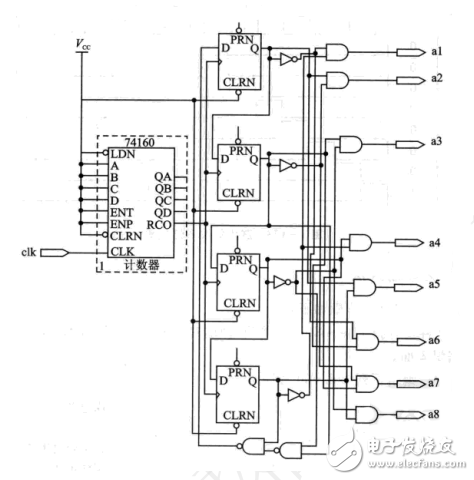

- 1 功能概述 流水廣告燈主要應(yīng)用于LED燈光控制。通過程序控制LED的亮和滅, 多個LED燈組成一個陣列,依次逐個點(diǎn)亮的時候像流水一樣,所以叫流水燈。由于其形成美觀大方的視覺效果,因此廣泛應(yīng)用于店鋪招牌、廣告、大型建筑夜間裝飾、景觀裝飾等。 在FPGA電路設(shè)計(jì)中,盡管流水燈的設(shè)計(jì)屬于比較簡單的入門級應(yīng)用,但是其運(yùn)用到的方法,是FPGA設(shè)計(jì)中最核心和最常用部分之一,是FPGA設(shè)計(jì)必須牢固掌握的基礎(chǔ)知識。從這一步開始,形成良好的設(shè)計(jì)習(xí)慣,寫出整潔簡潔的代碼,對于FPGA設(shè)計(jì)師來說至

- 關(guān)鍵字: Verilog FPGA

電子產(chǎn)品的無形敵人竟然是它

- 半個世紀(jì)以來,靜電在電子行業(yè)引起的著火、爆炸等事故不勝枚舉。僅美國電子行業(yè)每年因靜電造成的損失就高達(dá)幾百億美元,因此,靜電防護(hù)在減少損失、提升品質(zhì)和消費(fèi)效率方面具有重要的意義。 隨著集成電路行業(yè)的迅速發(fā)展,體積小、集成度高的器件越發(fā)受市場歡迎,這種需求也導(dǎo)致導(dǎo)線間間距越來越小,內(nèi)部氧化膜逐漸變薄,以至于制造過程中一些微小電壓就可能擊穿這些電子器件。而電子產(chǎn)品在生產(chǎn)、運(yùn)輸、儲存和轉(zhuǎn)運(yùn)等一系列過程中所產(chǎn)生的靜電電壓卻遠(yuǎn)遠(yuǎn)超過其耐壓值,這就可能造成器件的擊穿或失效,影響產(chǎn)品的可靠性。所以必須要重視靜電

- 關(guān)鍵字: 靜電 PCB

EMC問題-接地技巧及PCB工程師注意事項(xiàng)

- EMC問題 在布板的時候還應(yīng)該注意EMC的抑制哦!!這很不好把握,分布電容隨時存在!! 如何接地 PCB設(shè)計(jì)原本就要考慮很多的因素,不同的環(huán)境需要考慮不同的因素.另外,我不是PCB工程師,經(jīng)驗(yàn)并不豐富 地的分割與匯接 接地是抑制電磁干擾、提高電子設(shè)備EMC性能的重要手段之一。正確的接地既能提高產(chǎn)品抑制電磁干擾的能力,又能減少產(chǎn)品對外的EMI發(fā)射。 接地的含義 電子設(shè)備的“地”通常有兩種含義:一種是“大地”(安全地),另一種是“系統(tǒng)基準(zhǔn)地”(信號地)。接地就是指在系統(tǒng)與某個電位基準(zhǔn)面之間建

- 關(guān)鍵字: PCB EMC

教科書上絕對不會教的PCB布局秘籍

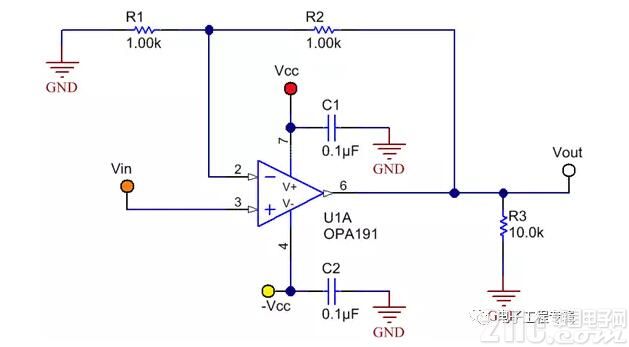

- 在電路設(shè)計(jì)過程中,應(yīng)用工程師往往會忽視印刷電路板(PCB)的布局。通常遇到的問題是,電路的原理圖是正確的,但并不起作用,或僅以低性能運(yùn)行。在本文中,我將向您介紹如何正確地布設(shè)運(yùn)算放大器的電路板以確保其功能、性能和穩(wěn)健性。 最近,我與一名實(shí)習(xí)生在利用增益為2V/V、負(fù)荷為10k?、電源電壓為+/-15V的非反相配置OPA191運(yùn)算放大器進(jìn)行設(shè)計(jì)。圖1所示為該設(shè)計(jì)的原理圖。 圖1:采用非反相配置的OPA191]OPA191原理圖 我讓實(shí)習(xí)生為該設(shè)計(jì)布設(shè)電路板,同時為他

- 關(guān)鍵字: PCB

高云半導(dǎo)體小蜜蜂家族GW1N系列新增兩款非易失性FPGA芯片成員

- 廣東高云半導(dǎo)體科技股份有限公司(以下簡稱“高云半導(dǎo)體”)今日宣布:高云半導(dǎo)體小蜜蜂家族GW1N系列新增GW1N-9和GW1N-6兩款非易失性FPGA芯片成員,并開始向客戶提供工程樣片及開發(fā)板。 作為小蜜蜂家族GW1N系列成員,GW1N-9和GW1N-6繼承了GW1N系列的低功耗、高性能、多用戶I/O、用戶邏輯資源豐富,支持高速LVDS接口,支持可隨機(jī)訪問的用戶閃存模塊等特點(diǎn);并在此基礎(chǔ)上,結(jié)合新的市場趨勢,創(chuàng)造性地集成了新的功能,使之成為全球首款集成了支持MIPI I3C和MIPI&nbs

- 關(guān)鍵字: 高云 FPGA

fsp:fpga-pcb介紹

您好,目前還沒有人創(chuàng)建詞條fsp:fpga-pcb!

歡迎您創(chuàng)建該詞條,闡述對fsp:fpga-pcb的理解,并與今后在此搜索fsp:fpga-pcb的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fsp:fpga-pcb的理解,并與今后在此搜索fsp:fpga-pcb的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司