EEPW首頁(yè) >>

主題列表 >>

fpga ip

fpga ip 文章 最新資訊

基于FPGA無(wú)線傳感器網(wǎng)絡(luò)MAC控制器的設(shè)計(jì)

- 摘要 給出了一種由FPGA實(shí)現(xiàn)的無(wú)線傳感器網(wǎng)絡(luò)MAC控制器的設(shè)計(jì)方法,采用自頂向下的方法設(shè)計(jì)各個(gè)模塊,并在QuartusII8.0完成了仿真,該控制器主要支持IEEE802.15.4協(xié)議。測(cè)試結(jié)果表明,該MAC控制器支持20~250 kbmi

- 關(guān)鍵字: FPGA MAC 無(wú)線傳感器網(wǎng)絡(luò) 控制器

基于FPGA的CAN總線控制器設(shè)計(jì)

- 摘要:使用Verilog HDL硬件描述語(yǔ)言完成了對(duì)CAN總線控制器的設(shè)計(jì),能夠?qū)崿F(xiàn)符合CAN2.0A協(xié)議的所有功能。本總線控制器的外部接口采用Altera公司開發(fā)的Avalon總線接口,增強(qiáng)了控制器的應(yīng)用靈活性。本設(shè)計(jì)使用Modelsim

- 關(guān)鍵字: FPGA CAN 線控 制器設(shè)計(jì)

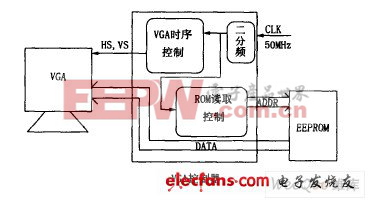

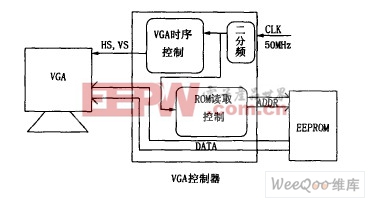

VGA圖形控制器的FPGA實(shí)現(xiàn)

- VGA圖形控制器的FPGA實(shí)現(xiàn),VGA(視頻圖形陣列)作為一種標(biāo)準(zhǔn)的顯示接口得到廣泛的應(yīng)用。利用FPGA 芯片和EDA 設(shè)計(jì)方法,可以因地制宜,根據(jù)用戶的特定需要,設(shè)計(jì)出針對(duì)性強(qiáng)的VGA 顯示控制器,不僅能夠大大降低成本,還可以滿足生產(chǎn)實(shí)踐中不斷變化

- 關(guān)鍵字: 實(shí)現(xiàn) FPGA 控制器 圖形 VGA

基于AVR單片機(jī)與FPGA的低頻數(shù)字式相位測(cè)量?jī)x

- 摘要:提出了以AVR ATmega128單片機(jī)和Altera公司的Cyclone系列EP1C3T100為核心的系統(tǒng)設(shè)計(jì)方案。分析了數(shù)字式低頻相位測(cè)量?jī)x的測(cè)量原理和測(cè)量誤差及其消除的方法。利用單片機(jī)強(qiáng)勁的運(yùn)算、控制功能和FPGA運(yùn)算速度快、資

- 關(guān)鍵字: 數(shù)字式相位 測(cè)量?jī)x 低頻 FPGA AVR 單片機(jī) 基于

恩智浦JenNet-IP軟件推動(dòng)“物聯(lián)網(wǎng)”的實(shí)現(xiàn)

- 恩智浦半導(dǎo)體NXP Semiconductors N.V. (NASDAQ:NXPI) 今日宣布將以開源授權(quán)方式提供其JenNet-IP超低功耗IEEE 802.15.4無(wú)線連接網(wǎng)絡(luò)層軟件,作為其“物聯(lián)網(wǎng)”實(shí)施計(jì)劃的一部分。近年來(lái),人們對(duì)物聯(lián)網(wǎng)的興趣與日俱增,在物聯(lián)網(wǎng)中,每臺(tái)設(shè)備都有一個(gè)IP地址,可以通過(guò)安全互聯(lián)網(wǎng)連接進(jìn)行監(jiān)視和控制。然而,物聯(lián)網(wǎng)普及所面臨的主要障礙是不同應(yīng)用都有不同的網(wǎng)絡(luò)軟件。通過(guò)發(fā)布基于開源授權(quán)的JenNet-IP網(wǎng)絡(luò)層軟件,并為眾多開發(fā)者和用戶提供支持,恩智浦志在簡(jiǎn)化為多種設(shè)備添加“

- 關(guān)鍵字: 恩智浦 JenNet-IP

基于FPGA 的VGA 圖形控制器的實(shí)現(xiàn)方法

- 本設(shè)計(jì)中存儲(chǔ)的圖像數(shù)據(jù)所采用的像素位深為3 位,共可顯示8種顏色。在實(shí)際應(yīng)用中,可以使用更大的存儲(chǔ)器,最終實(shí)現(xiàn)256 色圖像,乃至真彩色圖像的顯示。在此設(shè)計(jì)基礎(chǔ)上,通過(guò)使用SDRAM 等外部存儲(chǔ)器,利用DMA 控制方式,并且配合Altera 的nios 嵌入式軟核CPU ,可以在SOPC 開發(fā)平臺(tái)上最終實(shí)現(xiàn)兼容SVGA ,TVGA 標(biāo)準(zhǔn)等的更復(fù)雜顯示控制器。

- 關(guān)鍵字: 實(shí)現(xiàn) 方法 控制器 圖形 FPGA VGA 基于

fpga ip介紹

您好,目前還沒(méi)有人創(chuàng)建詞條fpga ip!

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga ip的理解,并與今后在此搜索fpga ip的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga ip的理解,并與今后在此搜索fpga ip的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司