基于AVR單片機與FPGA的低頻數字式相位測量儀

摘要:提出了以AVR ATmega128單片機和Altera公司的Cyclone系列EP1C3T100為核心的系統設計方案。分析了數字式低頻相位測量儀的測量原理和測量誤差及其消除的方法。利用單片機強勁的運算、控制功能和FPGA運算速度快、資源豐富的特點。主要介紹了系統的軟硬件設計。實踐表明,此方案設計的相位儀對低頻正弦波信號實現精確測頻和測相位差,具有處理速度快、穩定可靠、精度高等優點。

關鍵詞:數字相位儀;單片機;FPGA;誤差;頻率;相位差

在工業領域中經常要用到低頻數字式相位儀來精確測量兩信號之問的相位差,比如在電力系統、頻率特性的研究、激光測距等領域均有廣泛的應用,相位檢測的精度直接決定系統的整體性能。這就要求測量儀逐漸向智能化和測試自動化方向發展,本設計采用MCU和FPGA相結合的系統方案,以AVR單片機ATmega128和Altera公司的Cyclone系列EP1C3T100為核心,充分發揮各自的優勢,如AVR單片機先進的RISC結構和強勁的運算、控制功能,Altera公司的FPGA運算速度快、資源豐富以及易編程的特點,合理設計,此方案的相位儀具備速度快、穩定可靠、精度高等優點,而且容易實現“智能化”和“自動化”。

1 系統方案設計

1.1 測量方法的比較與選擇

目前相位測量的方法主要有兩種:

1)DFT測相法即將待測信號通過A/D轉換得到f(n),f(n)按離散傅里葉變換得出離散頻譜F(k),f(n)和F(k)為傅里葉變換對,通過運算得到兩路信號的基波相位,從而計算出相位差。DFT測相法的精度受限于ADC的采樣精度,需要高速ADC對信號進行過采樣,測量方案復雜,可以通過采集卡在計算機上實現虛擬儀器,所以主要應用在精度要求很高的場合和虛擬儀器中。

2)填充計數測相法 即兩路同頻的正弦信號經過信號整形電路后得到方波信號,方波信號經過鑒相器后,得到兩路輸入信號的相位差信號,用固定頻率的采樣脈沖進行填充并計數,從而計算出相位差。填充計數測相法主要應用在要求一定的精度,測量的頻率不是太高但實時性要求很強的場合,易于實現數字化和自動化,低頻數字相位儀適合用填充計數法。

填充計數測相法的基本算法:若正弦波整形后的方波信號頻率為f,周期為T,采樣脈沖周期為TC,方波一個周期內對采樣脈沖計數為,n則被測信號頻率f=1/T=1/nTC。同樣的方法測出兩個同頻正弦波起點之間的時間差為△t,則兩信號的相位差△θ=△t·360°/T。

1.2 系統方案的確定

由系統測量方法可知,數據需要采集、運算及顯示,考慮到Field Programmable Gate Array(FPGA)集成度高、I/O資源豐富、穩定可靠,選擇余地大,外圍元件很少,近年來價格下降等優勢,以及MCU良好的人機接口和運算控制功能,所以本系統由MCU和FPGA相結合構成測控主體。FPGA負責采集測頻和測相位差的脈沖信號,MCU負責讀FPGA采集的數據,計算待測信號頻率和相位差并在LCD上顯示。

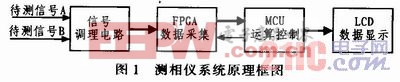

所以,系統由4個部分組成:待測信號調理電路、FPGA數據采集電路、MCU數據運算控制電路和LCD數據顯示電路,如圖1所示。

2 測量誤差的分析與消除

相位測量儀的完善設計,不僅要有合適的測量方法和系統實現方案,還需要著重分析誤差產生的原因和確定消除的方法。

1)填充時鐘頻率(即數據采樣信號)的影響與確定本相位測量儀的測頻范圍為20 Hz~20 kHz,相位差的范圍為△θ=0°~359.9°,相位差的顯示分辨率為0.1°,要求測量相位的絕對誤差≤2。

被測頻率20 Hz≤f≤20 kHz,則周期50μs≤T≤50 ms。

T=50 μs,絕對誤差取0.1°~2°。

則填充時鐘信號周期:0.1°x50 μs/360°≤TC≤2°x50 μs/360°即:1/72(μs)≤TC≤1/3.6(μs),可以得出填充時鐘頻率:

3.6 MHz≤fC≤72 MHz。

T=50ms內對TC=1/3.6(μs)的填充脈沖計數,計數值Nmin=180000≤218;對TC=1/72(μs)的填充脈沖計數,計數值Nmax=3600000≤ 222。

本設計考慮MCU的計算及分頻取得信號的方便,填充時鐘信號頻率fC=20 MHz,測量絕對誤差1°,FPGA在20 MHz時鐘信號作用下對待測信號周期和相位對應的時間差進行計數,FPGA采樣的二進制數據位為20 bit,可以保證測量的精度。

2)待測信號調理電路中零點漂移的影響與消除待測信號調理電路主要作用是把輸入信號整形變換成矩形波,通常采用過零比較器或者施密特觸發器。

過零比較器在零點電位附近可能會有振蕩,輸入信號在零點電位附近時,電壓比較器處于放大區,整形后的矩形波在邊沿會產生抖動,使系統無法進行測量。要消除這種抖動,可以采用施密特觸發器。為了保證測量的精度,施密特觸發器必須符合兩個條件:一是兩路被測信號幅度基本相等,二是門限電平要基本接近。

3)整形后方渡邊沿的陡峭程度的影響與消除信號經過整形后輸出的矩形脈沖信號直接送給FPGA,則FPGA不能立即獲取穩定的數字脈沖信號,就會使系統的精度受到很大影響。這主要是由于整形后方波邊沿不夠陡峭造成的。要解決此問題,一是選取具有較大壓擺率的器件,二是在比較器的后端加一級微分電路來提升脈沖信號的邊沿。

4)中低頻測量精度的影響與消除采用20 MHz數據采樣信號來循環計數被測信號的周期及相位差對應的時間差,精度達到0.05 μs,20位數字量的單位是0.05μs。利用被測信號刷新采樣計數,實現高頻多測量,低頻少測量,時間計數精確可靠,這樣,FPGA可以為MCU提供穩定的數據。

評論