- ? 美國國防預先研究計劃局射頻和微波技術專家正在與6家國防企業和大學合作,開發可編程射頻前端元件,以減少軍事通信、電子戰和信號情報系統(SIGINT)的成本和開發時間。

迄今為止,DARPA授權了6份關于“現場可編程門陣列射頻技術(RF-FPGA)”項目的合同。該項目旨在通過收發器鏈編程,跨不同應用程序重復使用同一組射頻前端元件。從根本上講, RF-FPGA項目試圖將現場可編程門陣列(FPGA)在數字計算方面的成功應用經驗轉移到射頻和微波技術,從而在廣泛應用中減少

- 關鍵字:

DARPA FPGA

- 在進行FPGA設計時,有很多需要我們注意的地方。具有好的設計風格才能做出好的設計產品,這一點是毋庸置疑的。那么,接下來,小編就帶大家一起來看看,再進行FPGA設計時,我們都要注意哪些呢? 一.命名風格: 1不

- 關鍵字:

FPGA 電子工程師 經驗

- 隨著高速數字系統的發展,高速串行數據被廣泛使用,內嵌高速串行接口的FPGA也得到大量應用,相應的高速串行信號質量的測試也越來越頻繁和重要。通常用示波器觀察信號波形、眼圖、抖動來衡量信號的質量,Xilinx提供的

- 關鍵字:

FPGA 集成式 比特 誤碼率測試儀

- 摘要:通過分析各種偽隨機序列生成方法,提出了一種基于M 序列的連續抽樣方法,可以生 成滿足自適應光學系統SPGD 控制算法要求的多路、相互獨立以及服從伯努利分布的偽隨機序 列。該方法適合于用FPGA 等超大規模集成

- 關鍵字:

FPGA 偽隨機序列 方法

- 隨著主流移動技術從2G、3G向LTE的演進過程中,移動業務逐漸由傳統語音轉向無線寬帶數據等為主的多業務發展,移動接入網絡的Abis和Iub接口也從傳統的TDM向分組化接口變化。因此,移動運營商如何高效傳輸承載快速增長

- 關鍵字:

提出 訴求 承載 RAN IP 協同

- 摘要:本設計基于DDS原理和FPGA技術按照順序存儲方式,將對正弦波、方波、三角波、鋸齒波四種波形的取樣數據依次全部存儲在ROM波形表里,通過外接設備撥扭開關和鍵盤控制所需波形信號的輸出,最終將波形信息顯示在LC

- 關鍵字:

FPGA DDS 信號發生器

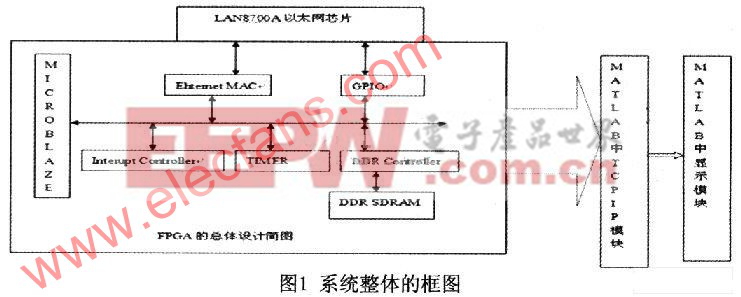

- O 引言 近年來,隨著信息技術的發展,網絡化日加普遍,以太網被廣泛應用到各個領域。例如在數據采集領域,一些小型監測設備需要增加網絡實現遠程數據傳輸的功能,只要那些設備上增加一個網絡接口并實現了TCP/IP協

- 關鍵字:

通信 Matlab 系統 研究 協議 基于 TCP IP FPGA

- 過去,TMOEM設計的儀器都是根據某種標準完成測試過程。這樣,當一個新的標準或修訂后的標準發布出來時,他...

- 關鍵字:

便攜式 測試設備 FPGA

- FPGA在廣播視頻中的應用, 1.時機

在世界范圍內,廣播視頻系統的需求都在逐年顯著增加,原因是以下的一些因素同時發生了作用:

可供觀眾選擇的廣播頻道的增加。世界范圍內,更多觀眾的選擇從很少的幾個頻道發展到幾百個頻道。

- 關鍵字:

應用 視頻 廣播 FPGA

- 1 引 言在ARM+FPGA系統結構中,實現基于ARM的嵌入式處理器和FPGA之間通信最簡單的方法就是通過異步串行接口EIARS232C。考慮選用集成有UART(Universal Asynchronous Receiver / TraNSmitter )控制器的嵌入式處理器

- 關鍵字:

UART FPGA

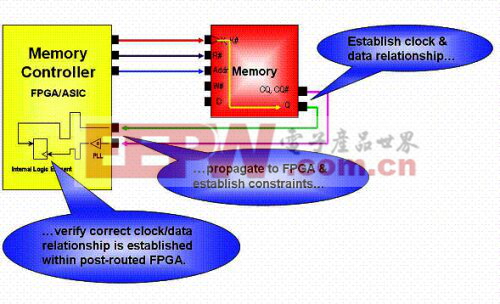

- 如何有效的管理FPGA設計中的時序問題, 當

二、導言 FPGA的設計與高速接口技術可以幫助你滿足今天的市場要求,但也提出了一些有趣的設計挑戰。為了確保存儲器接口的數據傳輸準確,在超過200兆赫茲以上,進行時序分析將發揮更突出的作用,以

- 關鍵字:

時序 問題 設計 FPGA 有效 管理 如何

- 摘要:為了消除空間環境中單粒子翻轉(SEU)的影響,目前星載計算機中均對RAM存儲單元采用檢錯糾錯(EDAC)設計。隨著FPGA在航天領域的廣泛應用,FPGA已成為EDAC功能實現的最佳硬件手段。本文介紹了EDAC的編碼和實現,提出一

- 關鍵字:

FPGA EDAC 星載 計算機

- 摘要:現在嵌入式系統的功能越來越集合化,需要控制大量外設。外設模塊普遍采用UART作為通信接口,但是通常處理器都會自帶一個UART串口。實際應用中一個串口往往不夠用,需要對系統進行擴展。本文所介紹的就是以FPGA為實

- 關鍵字:

FPGA UART 總線設計

- 摘要:為了提高水聲傳感器網絡通信系統試驗和算法研究的效率,水聲傳感器網絡節點需要具有水聲通信的原始波形數據的記錄功能。本文設計了一種水聲信號采樣存儲系統,實現了數據變速率AD采集、數據環形存儲、數據連續

- 關鍵字:

FPGA 水聲信號 采樣 存儲

- 摘要:在時差定位(TDOA)技術中,高精度的時差測量是準確定位的關鍵。針對這一需要, 提出一種基于FPGA 的高精度時差測量系統的實現方案。本系統的時差測算單元以Altera 公司Cyclone 系列的EP1C3T144 芯片為核心,并提

- 關鍵字:

FPGA 高精度 時差測量 系統設計

fpga ip介紹

您好,目前還沒有人創建詞條fpga ip!

歡迎您創建該詞條,闡述對fpga ip的理解,并與今后在此搜索fpga ip的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473