基于FPGA 的UART 擴展總線設(shè)計和應(yīng)用

摘要:現(xiàn)在嵌入式系統(tǒng)的功能越來越集合化,需要控制大量外設(shè)。外設(shè)模塊普遍采用UART作為通信接口,但是通常處理器都會自帶一個UART串口。實際應(yīng)用中一個串口往往不夠用,需要對系統(tǒng)進行擴展。本文所介紹的就是以FPGA為實現(xiàn)方式的UART擴展總線設(shè)備的邏輯設(shè)計以及相關(guān)的驅(qū)動程序的設(shè)計。

本文引用地址:http://www.104case.com/article/189976.htm1 引言

在嵌入式領(lǐng)域,由于UART 具有操作簡單、工作可靠、抗干擾強、傳輸距離遠(yuǎn)(組成 485 網(wǎng)絡(luò)可以傳輸1,200 米以上),設(shè)計人員普遍認(rèn)為UART 是從CPU 或微控制器向系統(tǒng)的 其他部分傳輸數(shù)據(jù)的最佳方式,因此它們被大量地應(yīng)用在工業(yè)、通信和家電控制等嵌入式領(lǐng) 域。而通常處理器都會自帶一個UART 串口,實際應(yīng)用中一個串口往往不夠用,需要進行 UART 串口擴展。而本文在分析了片內(nèi)總線技術(shù)和UART 的工作原理的基礎(chǔ)上了實現(xiàn)UART 總線設(shè)備的設(shè)計,使主控芯片可以控制4~6 個外圍設(shè)備。

本文中的嵌入式系統(tǒng)由AT91ARM9200 處理器、Linux 操作系統(tǒng)和ALTERA 公司的 ACEX 系列的EP1K 所組成。

2 EP1K 的邏輯設(shè)計

設(shè)計所要實現(xiàn)的功能是 AT91ARM9200 處理器通過EP1K 控制多個帶有UART 接口的 外設(shè)。EP1K 中包含了多個邏輯模塊如圖1 所示,為了實現(xiàn)多個模塊間的互聯(lián)就需要片內(nèi)總 線的支持,而本文采用的是WISHBONE 片內(nèi)總線規(guī)范。

2.1 WISHBONE 總線設(shè)計

WISHBONE采用主從結(jié)構(gòu),也稱之為SLAVE/MASTER 結(jié)構(gòu)。主單元MASTER 是發(fā)起 與從單元SLAVE 之間的數(shù)據(jù)傳輸,MASTER 和SLAVE 通過握手協(xié)議來實現(xiàn)可靠通信的。

WISHBONE 總線架構(gòu)提供了四種不同的互聯(lián)方式:點對點(Point-to-point)、數(shù)據(jù)流(Data flow)、共享總線(Shared bus)和交叉開關(guān)(Crossbar switch)。為了實現(xiàn)單個MASTER 和多個SLAVE 的設(shè)計要求,同時要求總線結(jié)構(gòu)占用較少的邏輯單元,所以采用了共享總線 的互聯(lián)方式。

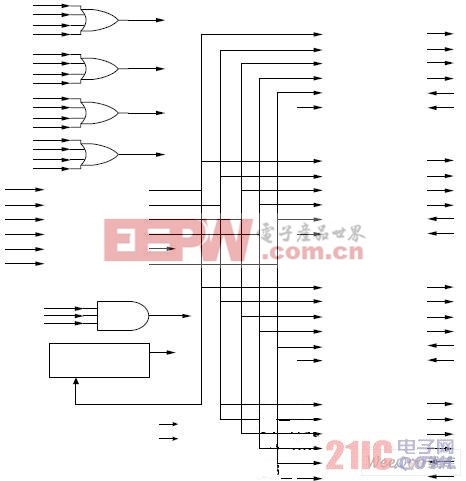

共享總線應(yīng)包括 MASTER、SLAVE、INTERCON 和SYSCON 四個部分。MASTER 和 SLAVE 是實現(xiàn)總線信號與IP 核的信號轉(zhuǎn)換,INTERCON 用于MATER 和Slave 的信號互聯(lián), 而SYSCON 則提供穩(wěn)定的時鐘信號和復(fù)位信號。總線邏輯結(jié)構(gòu)如圖2 所示,因為只有一個 MASTER,設(shè)計時就省略了對總線使用權(quán)的總裁。MASTER 的地址和數(shù)據(jù)總線分別與四個 SLAVE 相聯(lián),其它的控制信號也都是直接相連,而SLAVE 的選通是通過stb 信號實現(xiàn)。 SLAVE 的stb 信號是由地址譯碼產(chǎn)生SLAVE 選擇信號s_sel、m_cyc 和m_stb 三個信號相與 的結(jié)果。所選通的SLAVE 將ack 信號置1 表明一個數(shù)據(jù)傳輸周期的正常結(jié)束并將數(shù)據(jù)鎖存 或發(fā)送到總線上,而err 信號置1 表示非正常結(jié)束,rty 信號置1 表示要求數(shù)據(jù)重發(fā)。

圖 2 WISHBONE 總線的邏輯結(jié)構(gòu)圖

總線的詳細(xì)設(shè)計過程請參考 WISHBONE SoC Architecture Specification, Revision B.3,而 MASTER 和SLAVE 的設(shè)計可以參考OpenCores 的網(wǎng)站上相關(guān)設(shè)計。

評論