fpga ip 文章 最新資訊

基于FPGA的手勢(shì)識(shí)別系統(tǒng)研究

- 相比于傳統(tǒng)鍵盤鼠標(biāo)人機(jī)交互模式,手勢(shì)識(shí)別具有更大發(fā)展?jié)摿Γ疚南却罱艘粋€(gè)有關(guān)手勢(shì)識(shí)別的框架,然后再和FPGA的硬件技術(shù)相關(guān)聯(lián),將FPGA融入手勢(shì)識(shí)別之中,并設(shè)計(jì)自己的手勢(shì)識(shí)別算法,使得能夠在平臺(tái)上得以實(shí)現(xiàn)。

- 關(guān)鍵字: 202306 FPGA 手勢(shì)識(shí)別

CEVA將在上海世界移動(dòng)通信大會(huì)展示消費(fèi)類電子用芯片和軟件IP

- 全球領(lǐng)先的無線連接和智能感知技術(shù)及共創(chuàng)解決方案的授權(quán)許可廠商CEVA, Inc.(納斯達(dá)克股票代碼:CEVA)參加2023年6月28至30日在上海舉辦的世界移動(dòng)通信大會(huì)。在這次展會(huì)上,CEVA團(tuán)隊(duì)將與SoC和OEM客戶面對(duì)面溝通交流,探討最新的技術(shù)創(chuàng)新,并介紹如何充分利用CEVA IP開發(fā)無線連接和智能感知應(yīng)用以實(shí)現(xiàn)產(chǎn)品設(shè)計(jì)目標(biāo)。 CEVA將在行政會(huì)議室展示用于邊緣AI、5G、計(jì)算機(jī)視覺、空間音頻(spatial-audio)和物聯(lián)網(wǎng)連接的最新解決方案,包括: ● 邊緣AI推

- 關(guān)鍵字: CEVA 上海世界移動(dòng)通信大會(huì) IP

Microchip發(fā)布中端FPGA工業(yè)邊緣協(xié)議棧、核心庫(kù)IP和轉(zhuǎn)換工具

- 這些新工具使得轉(zhuǎn)向使用PolarFire? FPGA和片上系統(tǒng)(SoC)FPGA變得比以往更容易 隨著智能邊緣設(shè)備對(duì)能效、安全性和可靠性提出新要求,系統(tǒng)架構(gòu)師和設(shè)計(jì)工程師不得不尋找新的解決方案。Microchip Technology Inc.(美國(guó)微芯科技公司)今日宣布推出新的開發(fā)資源和設(shè)計(jì)服務(wù),以幫助系統(tǒng)設(shè)計(jì)人員轉(zhuǎn)向使用PolarFire FPGA和SoC,包括業(yè)界首款中端工業(yè)邊緣協(xié)議棧、可定制的加密和軟知識(shí)產(chǎn)權(quán)(IP)啟動(dòng)庫(kù),以及將現(xiàn)有FPGA設(shè)計(jì)轉(zhuǎn)換為PolarFire器件的新工具。&n

- 關(guān)鍵字: Microchip FPGA 工業(yè)邊緣協(xié)議棧

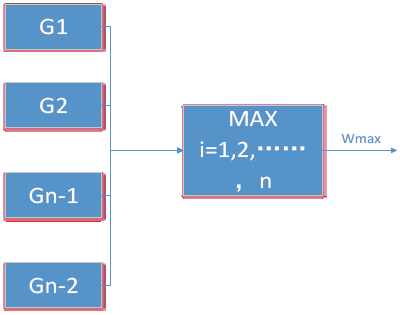

先進(jìn)的系統(tǒng)控制FPGA為您帶來全新可能

- 在過去的幾年里,我們見證了人工智能模型的革命性發(fā)展,尤其是隨著市場(chǎng)上生成式人工智能工具的興起(如OpenAI的ChatGPT、谷歌的Bard和其他每天都在推出的新模型),這種發(fā)展比以往任何時(shí)候都要迅猛。AI模型包括自然語言處理、計(jì)算機(jī)視覺和其他工作類型,這些任務(wù)將推動(dòng)AI的進(jìn)一步發(fā)展,但這也需要系統(tǒng)基礎(chǔ)設(shè)施跟上步伐,因?yàn)橄到y(tǒng)控制復(fù)雜性與日俱增,同時(shí)對(duì)存儲(chǔ)容量、系統(tǒng)控制接口速度和帶寬要求也不斷增長(zhǎng)。隨著這些技術(shù)創(chuàng)新帶來的計(jì)算吞吐量的顯著提高,先進(jìn)、復(fù)雜的系統(tǒng)設(shè)計(jì)和系統(tǒng)控制架構(gòu)的需求和重要性只會(huì)進(jìn)一步增加。這

- 關(guān)鍵字: 系統(tǒng)控制 FPGA

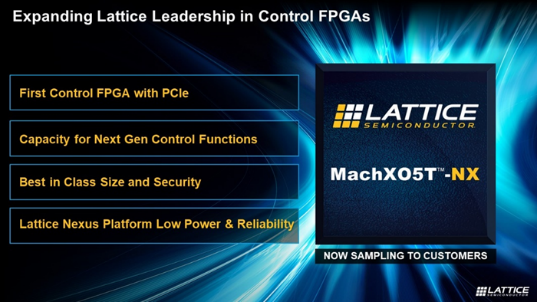

利用VectorBlox開發(fā)工具包在PolarFire FPGA實(shí)現(xiàn)人工智能

- 隨著人工智能、機(jī)器學(xué)習(xí)技術(shù)和物聯(lián)網(wǎng)的興起,人工智能的應(yīng)用開始逐漸轉(zhuǎn)移到收集數(shù)據(jù)的邊緣裝置。為縮小體積、減少產(chǎn)熱、提高計(jì)算性能,這些邊緣應(yīng)用需要節(jié)能型的解決方案。Microchip的智能嵌入式視覺解決方案,致力于讓軟件開發(fā)人員可以更方便地在PolarFire?現(xiàn)場(chǎng)可編程門陣列(FPGA)內(nèi)執(zhí)行人工智能的模型,進(jìn)而滿足邊緣應(yīng)用對(duì)節(jié)能型推理功能日益增長(zhǎng)的需求。作為Microchip嵌入式解決方案組合的重要新成員,VectorBlox?加速器軟件開發(fā)工具包(SDK)可幫助軟件開發(fā)人員在不學(xué)習(xí)FPGA工具流程的前提

- 關(guān)鍵字: VectorBlox 開發(fā)工具包 PolarFire FPGA 人工智能

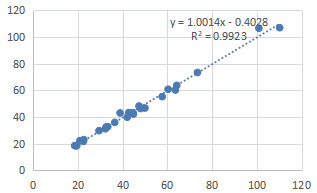

一種用于溫濕度批量自動(dòng)校準(zhǔn)系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

- 設(shè)計(jì)了一種基于FPGA的多UART擴(kuò)展系統(tǒng),用來批量采集溫濕度傳感器的數(shù)據(jù),簡(jiǎn)單介紹FPGA擴(kuò)展UART的方法。上位機(jī)控制程序?qū)邮盏降呐繙貪穸葦?shù)據(jù)進(jìn)行自動(dòng)分選、存儲(chǔ),并實(shí)現(xiàn)批量自動(dòng)線性校準(zhǔn)。溫濕度校準(zhǔn)前后的測(cè)量數(shù)據(jù)表明,設(shè)備數(shù)據(jù)的一致性得到很大提升。此設(shè)計(jì)已成功應(yīng)用于生產(chǎn)校準(zhǔn)系統(tǒng)中,方便快捷。此設(shè)計(jì)方法和思想可以推廣到其他需要批量數(shù)據(jù)采集,批量數(shù)據(jù)自動(dòng)處理的場(chǎng)合。

- 關(guān)鍵字: 202305 批量 自動(dòng)校準(zhǔn) FPGA UART擴(kuò)展 線性擬合

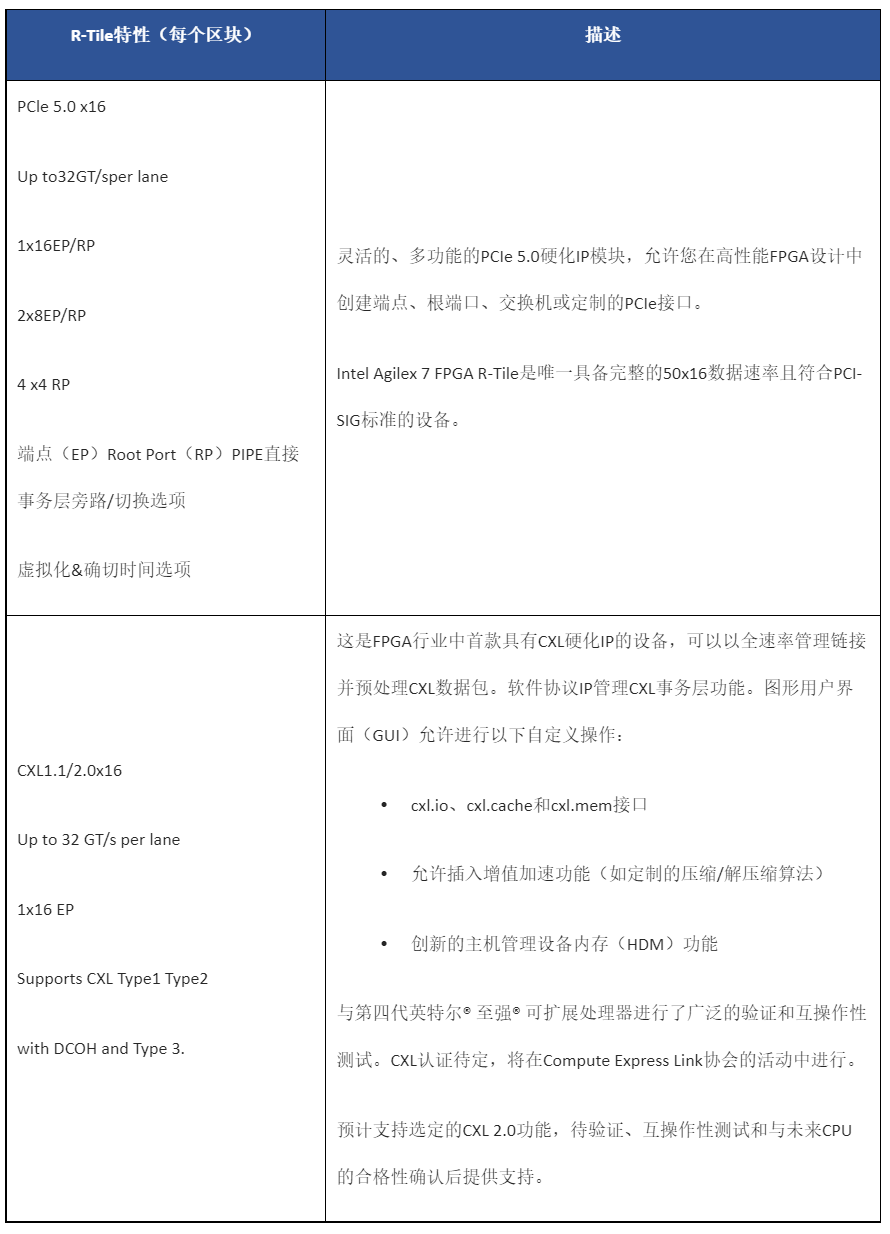

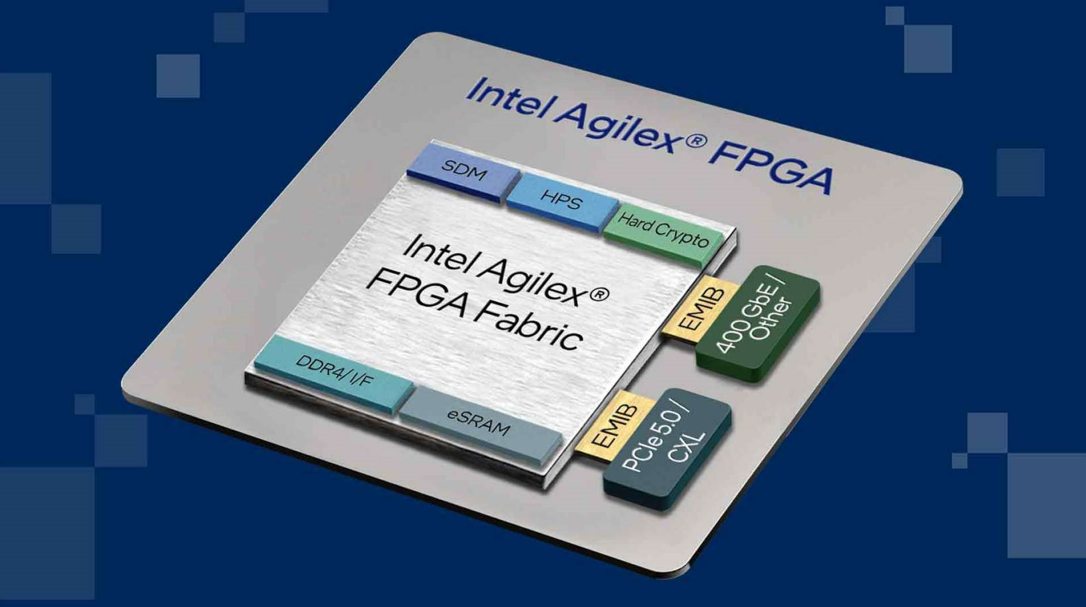

英特爾發(fā)布首款具有PCIe5.0和CXL功能的FPGA

- 當(dāng)?shù)貢r(shí)間5月22日,英特爾可編程解決方案事業(yè)部宣布,符合量產(chǎn)要求的英特爾Agilex?7 R-tile正在批量交付。該設(shè)備是首款具備PCIe 5.0和CXL功能的FPGA,同時(shí)這款FPGA亦是唯一一款擁有支持上述接口所需的硬化知識(shí)產(chǎn)權(quán)(IP)的產(chǎn)品。英特爾表示,面對(duì)時(shí)間、預(yù)算和功耗所帶來的限制,包括數(shù)據(jù)中心、電信和金融服務(wù)在內(nèi)的各行業(yè)組織都將FPGA視為靈活、可編程的,以及高效的解決方案。使用Agilex 7 R-Tile,客戶可以將FPGA與諸如第四代英特爾至強(qiáng)可擴(kuò)展處理器等進(jìn)行無縫銜接,并通過

- 關(guān)鍵字: 英特爾 PCIe5.0 CXL FPGA

英特爾Agilex 7 FPGA R-Tile現(xiàn)已量產(chǎn),為CPU提供領(lǐng)先的帶寬

- 在技術(shù)創(chuàng)新的推動(dòng)下,從邊緣計(jì)算到云的新連接和處理模型也在高速發(fā)展,隨之而來的,則是對(duì)靈活硬件解決方案與日俱增的需求。隨著市場(chǎng)上對(duì)帶寬的要求不斷增加,對(duì)更快、更靈活的設(shè)備的需求也日益迫切。而于近期推出的英特爾Agilex? 7 FPGA R-Tile,憑借其高帶寬接口和靈活的可編程邏輯,能夠滿足行業(yè)發(fā)展需求。目前,基于R-Tile的英特爾Agilex 7 FPGA正在量產(chǎn)。近年來,F(xiàn)PGA 加速器在市場(chǎng)上的應(yīng)用率穩(wěn)步增長(zhǎng),而隨著配備R-Tile的FPGA 的推出,更高性能的加速器也隨之而來。FPGA 加速器

- 關(guān)鍵字: 英特爾 Agilex FPGA

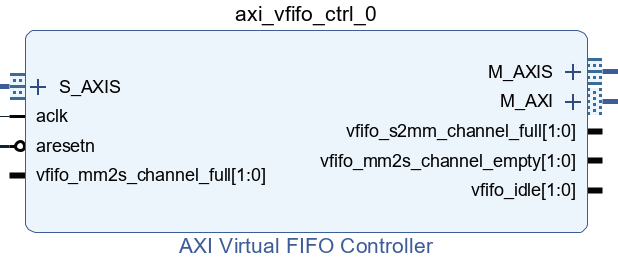

基于PCIe+X86系統(tǒng)的毫米波信號(hào)實(shí)時(shí)處理研究及FPGA實(shí)現(xiàn)*

- 為了滿足毫米波5G信號(hào)采集傳輸控制系統(tǒng)中對(duì)前端射頻芯片的控制以及5G數(shù)據(jù)到上位機(jī)的高速傳輸?shù)男枨螅O(shè)計(jì)了一套基于FPGA的高速采集系統(tǒng)。實(shí)現(xiàn)了基帶數(shù)據(jù)的高速傳輸,測(cè)試結(jié)果驗(yàn)證了設(shè)計(jì)方案的可行性。該系統(tǒng)可允許用戶通過PCIe總線訪問FPGA中的用戶配置寄存器,同時(shí)該系統(tǒng)可對(duì)前端射頻產(chǎn)生的不高于4 GB/s的連續(xù)或非連續(xù)上行數(shù)據(jù)進(jìn)行實(shí)時(shí)采集,同時(shí)可以將上位機(jī)中的下行數(shù)據(jù)以不少于4 GB/s的速率寫入FPGA側(cè)的DDR4。

- 關(guān)鍵字: 202305 5G NR 毫米波 PCIe FPGA X86

用于多時(shí)鐘域 SoC 和 FPGA 的同步器技術(shù)

- 通常,傳統(tǒng)的雙觸發(fā)器同步器用于同步單比特電平信號(hào)。如圖1和圖2所示,觸發(fā)器A和B1工作在異步時(shí)鐘域。CLK_B 時(shí)鐘域中的觸發(fā)器 B1 對(duì)輸入 B1-d 進(jìn)行采樣時(shí),輸出 B1-q 有可能進(jìn)入亞穩(wěn)態(tài)。但在 CLK_B 時(shí)鐘的一個(gè)時(shí)鐘周期期間,輸出 B1-q 可能穩(wěn)定到某個(gè)穩(wěn)定值。常規(guī)二觸發(fā)器同步器通常,傳統(tǒng)的雙觸發(fā)器同步器用于同步單比特電平信號(hào)。如圖1和圖2所示,觸發(fā)器A和B1工作在異步時(shí)鐘域。CLK_B 時(shí)鐘域中的觸發(fā)器 B1 對(duì)輸入 B1-d 進(jìn)行采樣時(shí),輸出 B1-q 有可能進(jìn)入亞穩(wěn)態(tài)。但在 CLK

- 關(guān)鍵字: SoC FPGA

英特爾發(fā)布首款支持PCIe 5.0和CXL功能的Agilex 7 FPGA R-Tile

- 英特爾可編程解決方案事業(yè)部今日宣布,符合量產(chǎn)要求的英特爾Agilex? 7 R-tile正在批量交付。該設(shè)備是首款具備PCIe 5.0和CXL功能的FPGA,同時(shí)這款FPGA亦是唯一一款擁有支持上述接口所需的硬化知識(shí)產(chǎn)權(quán)(IP)的產(chǎn)品。英特爾公司副總裁兼可編程解決方案事業(yè)部總經(jīng)理Shannon Poulin表示:"客戶需要尖端技術(shù)提供所需的可擴(kuò)展性和定制化服務(wù),這不僅可以有效地管理當(dāng)前的工作負(fù)載,同時(shí)能夠隨著其需求變化來調(diào)整功能。英特爾Agilex產(chǎn)品以客戶所需的速度、功耗和功能支持可編程創(chuàng)新,

- 關(guān)鍵字: 英特爾 PCIe 5.0 CXL功能 Agilex 7 FPGA

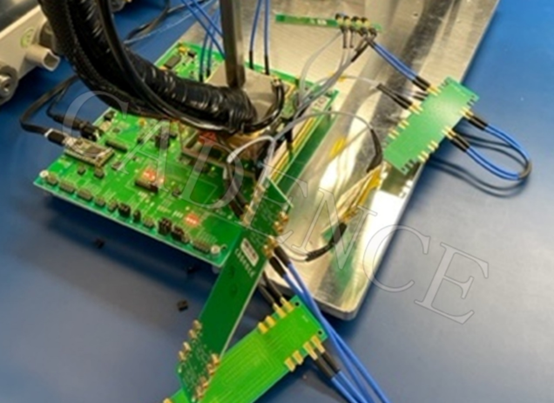

Cadence發(fā)布面向TSMC 3nm工藝的112G-ELR SerDes IP展示

- 3nm 時(shí)代來臨了!Cadence 在 2023 年 TSMC 北美技術(shù)研討會(huì)期間發(fā)布了面向臺(tái)積電 3nm 工藝(N3E)的 112G 超長(zhǎng)距離(112G-ELR)SerDes IP 展示,這是 Cadence 112G-ELR SerDes IP 系列產(chǎn)品的新成員。在后摩爾時(shí)代的趨勢(shì)下,F(xiàn)inFET 晶體管的體積在 TSMC 3nm 工藝下進(jìn)一步縮小,進(jìn)一步采用系統(tǒng)級(jí)封裝設(shè)計(jì)(SiP)。通過結(jié)合工藝技術(shù)的優(yōu)勢(shì)與 Cadence 業(yè)界領(lǐng)先的數(shù)字信號(hào)處理(DSP)SerDes 架構(gòu),全新的 112G-ELR

- 關(guān)鍵字: Cadence TSMC 3nm工藝 SerDes IP

芯原股份:公司的神經(jīng)網(wǎng)絡(luò)處理器IP系列產(chǎn)品可廣泛適用于AIoT、智慧汽車等應(yīng)用場(chǎng)景

- 2023年5月8日,芯原股份(688521.SH)在互動(dòng)平臺(tái)表示,芯原用于人工智能的神經(jīng)網(wǎng)絡(luò)處理器IP(NPU)業(yè)界領(lǐng)先,已經(jīng)在10多個(gè)領(lǐng)域、60多家客戶的110多款芯片中被采用。根據(jù)目前市場(chǎng)的需求,芯原基于自身神經(jīng)網(wǎng)絡(luò)處理器IP可伸縮可擴(kuò)展的特性,已發(fā)展了覆蓋從高性能云計(jì)算到低功耗邊緣計(jì)算的垂直解決方案;同時(shí)還推出了從攝像頭輸入到顯示器輸出的完整智能像素解決方案。因此,在人工智能領(lǐng)域,芯原的神經(jīng)網(wǎng)絡(luò)處理器IP系列產(chǎn)品可廣泛適用于包括智慧物聯(lián)網(wǎng)(AIoT)、智慧汽車、智慧可穿戴、智慧家居、視頻數(shù)據(jù)中心、智

- 關(guān)鍵字: 芯原股份 IP 神經(jīng)網(wǎng)絡(luò)處理器IP

楷登電子成功流片基于臺(tái)積電N3E工藝的16G UCIe先進(jìn)封裝IP

- 近日,楷登電子(Cadence)宣布基于臺(tái)積電3nm(N3E)工藝技術(shù)的Cadence? 16G UCIe? 2.5D先進(jìn)封裝IP成功流片。該IP采用臺(tái)積電3D Fabric? CoWoS-S硅中介層技術(shù)實(shí)現(xiàn),可提供超高的帶寬密度、高效的低功耗性能和卓越的低延遲,非常適合需要極高算力的應(yīng)用。據(jù)悉,楷登電子目前正與許多客戶合作,來自N3E測(cè)試芯片流片的UCIe先進(jìn)封裝IP已開始發(fā)貨并可供使用。這個(gè)預(yù)先驗(yàn)證的解決方案可以實(shí)現(xiàn)快速集成,為客戶節(jié)省時(shí)間和精力。

- 關(guān)鍵字: 楷登電子 臺(tái)積電 N3E UCIe 先進(jìn)封裝 IP

fpga ip介紹

您好,目前還沒有人創(chuàng)建詞條fpga ip!

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga ip的理解,并與今后在此搜索fpga ip的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga ip的理解,并與今后在此搜索fpga ip的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司