基于PCIe+X86系統的毫米波信號實時處理研究及FPGA實現*

*基金項目:蚌埠市科技計劃項目,高性能5G增強移動寬帶通信矢量信號發生器

本文引用地址:http://www.104case.com/article/202305/446926.htm0 引言

隨著移動通信的迅猛發展及5G NR 技術的成熟,低頻頻譜資源的開發已經非常成熟,剩余的低頻頻譜資源已經不能滿足5G 時代10 Gbit/s 的峰值速率要求,因此未來5G 系統需要在毫米波頻段上尋找可用的頻譜資源。隨著全球移動通信技術向著網絡化和寬帶化趨勢發展,5G 商用的基站和手機也已近開始部署與批量生產。現在儀表除了能夠分析6 GHz 以下頻率的信號以外,還需要分析微波、毫米波等波形。毫米波傳輸的技術難點主要在于5G 極高速的傳輸速率導致信號寬帶和基帶信號處理速度都將大大增加,對極高速數據流的實時處理和解析使得測試變得更加困難,作為測試技術的先行者,測試儀表5G功能毫米波測試技術開發也已提上日程[1]。

目前的高速數據傳輸系統中數據之所以可以高速、穩定的進行傳輸,總線技術在其中起到了很大的作用。早期的總線是以PCI 總線為代表的并行總線,并行總線因其并行結構的缺陷,導致傳輸速率無法進一步提高。PCIe 總線作為其中代表,在帶寬、性能、時延、功耗、可靠性等方面有著卓越的表現,為高速數據傳輸系統提供了堅實可靠的技術支持。

賽靈思公司為其FPGA 提供了PCIe IP 核,提供了多種用戶接口,可以大大降低設計成本,縮短整個項目的研發周期。隨著人們近年來對5G 移動通信和人工智能等領域的深入研究,越來越多的科研人員基于FPGA高性能運算平臺進行課題研究,但是運算過程中出現的海量數據傳輸問題成為需要克服的問題,所以對基于FPGA 的PCIe 高速數據傳輸系統進行研究有著重要的研究價值。

基帶接收處理模塊是滿足多通道接收、不同系統帶寬、不同子載波間隔、多用戶基帶接收的指標要求,完成參數靈活可配單用戶、多用戶基帶信號接收功能,滿足5G 終端的低延時、高效率、高質量的處理能力。FPGA 是現階段實現采用的主流方式,具有較強的處理數字能力,設計采用Xilinx 公司的FPGA 芯片作為主要的實現平臺。為了實現基帶數據成功采集后的實時分析,采用PCIe 將FPGA 數據傳輸給上位機進行處理,突破高速信號不易實時分析的難題。

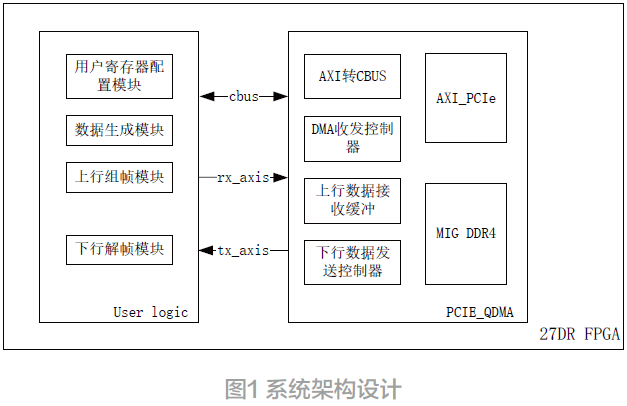

1 系統架構

為了滿足5G 信號采集傳輸控制系統中對前端射頻芯片的控制以及5G 數據到上位機的高速傳輸的需求。本設計實現了一套基于FPGA 的高速采集系統。該系統可允許用戶通過PCIe 總線訪問FPGA 中的用戶配置寄存器,同時該系統可對前端射頻產生的不高于4 GB/s(若使用多通道,則全部通道的累加帶寬不高于4 GB/s)的連續或非連續上行數據進行實時采集,同時可以將上位機中的下行數據以不低于4 GB/s 的速率寫入FPGA 側的DDR4,并通過控制相應的發送寄存器將DDR4 中的數據以循環或單次的形式發送給射頻端。

系統設計主要分為兩部分:用戶側邏輯和PCIe_DMA 傳輸側邏輯。

1.1 用戶側邏輯

1)模擬數據產生模塊。用戶可通過配置寄存器來產生4 種帶寬模式的模擬數據。

2)用戶寄存器配置模塊。用戶可通過cbus 接口讀寫用戶寄存器。通過用戶寄存器配置各類參數。

3)上行組幀模塊。根據用戶配置的四種模式,對模擬數據產生模塊生成的數據添加相對應的32 字節幀頭和32 字節幀尾。

4)下行解幀模塊。該部分由用戶自己實現,對DMA收發控制器發出的下行數據進行解幀。

1.2 PCIe_DMA傳輸側邏輯

1)AXI 轉CBUS 模塊。該模塊實現用戶通過PCIe總線的AXI 接口訪問用戶端的CBUS 接口。

2)DMA 收發控制模塊。該模塊提供1 路AXIS 接收接口,供用戶接入上行數據;提供1 路AXI 接口供用戶讀寫寄存器;提供1 路AXI 接口,供用戶將下行數據寫入DDR4。提供1 路傳統中斷。

3)上行數據接收緩沖模塊。該模塊實現1 個數據虛通道,使上行數據通過DDR4 緩存后再發送給DMA收發控制模塊。

4)下行數據發送控制器模塊。該模塊實現用戶通過配置寄存器完成DDR4 中任意地址任意長度的下行數據循環發送和單次發送。

5)AXI PCIE 橋模塊。該模塊使用XILINX 官方IP核實現,用戶可通過AXI 接口實現對上位機的內存讀寫訪問。

6)MIG DDR4 模塊。該模塊實現上行數據和下行數據的DDR4 緩存。

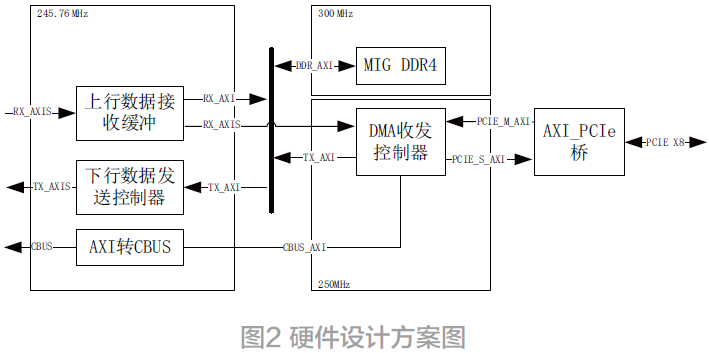

2 FPGA詳細設計方案

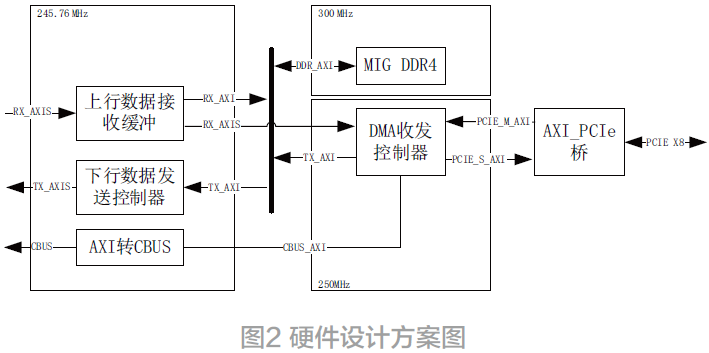

PCIe 數據采集DMA 控制器模塊(PCIE_DMA) 是該采集系統的核心模塊,圖2 為該模塊的邏輯設計框圖。上行數據流向描述如下:上位機用戶通過AXI_PCIE橋的PCIE_M_AXI 接口讀寫用戶寄存器,控制上行模擬數據的產生;上行模擬數據通過RX_AXIS 接口寫入上行數據接收緩沖,經過FPGA 板載DDR4 做緩沖后通過RX_AXIS 接口寫入DMA 收發控制器;DMA收發控制器模塊將收到的數據通過PCIE_S_AXI 接口寫入上位機內存。下行數據流向描述如下:上位機用戶通過AXI_PCIE 橋的PCIE_M_AXI 接口讀寫DMA收發控制器中的發送配置寄存器;DMA 收發控制器通過PCIE_S_AXI 接口從上位機獲取下行數據并通過TX_AXI接口寫入FPGA 板載DDR4;上位機用戶通過AXI_PCIE 橋的PCIE_M_AXI 接口讀寫用戶側的發送地址、發送長度、發送周期等寄存器;下行數據發送控制器根據用戶側的發送地址、發送長度、發送周期等寄存器從板載DDR4 中讀取數據并通過TX_AXIS 接口發送到次級模塊。

3 數據傳輸設計

3.1 上行數據緩沖模塊

3.1.1 輸入輸出接口

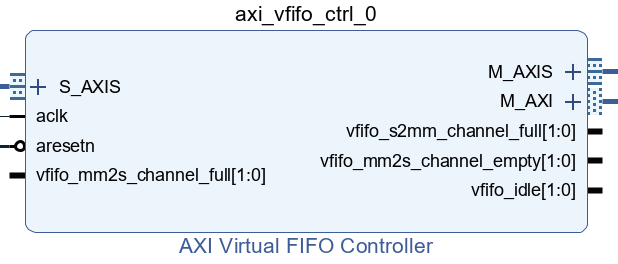

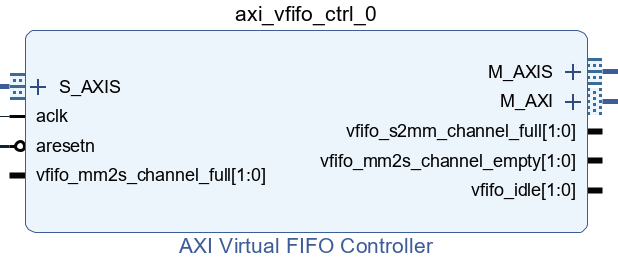

圖3

該模塊為上行數據緩沖模塊。該模塊利用vfifo 控制器實現,vfifo 控制器本質是兩個DMA。第1 個DMA 將S_AXIS 收到的上行數據轉換成M_AXI 接口寫入DDR4做緩存,第2 個DMA 通過M_AXI 接口將數據從DDR4中讀出來并轉換成M_AXIS 接口送入次級處理模塊。該模塊主要為了實現瞬時帶寬較高的情況下,上行數據的緩存。

3.2 下行數據發送控制器

3.2.1 輸入輸出接口

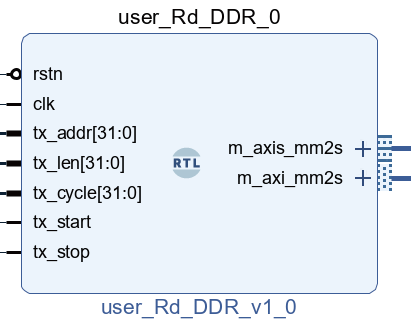

圖4

該模塊是下行數據發送控制器模塊,此模塊可幫助用戶通過tx_addr、tx_len、tx_cycle、tx_start、tx_stop來實現從DDR4 中讀取任意長度的數據并以單次或者多次或者循環發送的方式發送到次級模塊。具體接口定義如下。

tx_addr :發送地址。

tx_len:發送長度。

tx_cycle:循環發送次數,0 為循環發送,1-n 為固定次數發送。

tx_start:發送開始。

tx_stop:循環發送停止。

m_axi_mm2s:通過AXI 接口從DDR4 中讀取數據。

m_axis_mm2s:通過AXIS 接口將下行數據發送給用戶。

3.3 AXI轉CBUS

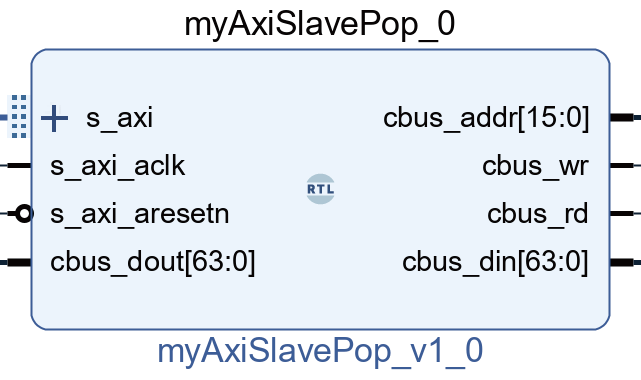

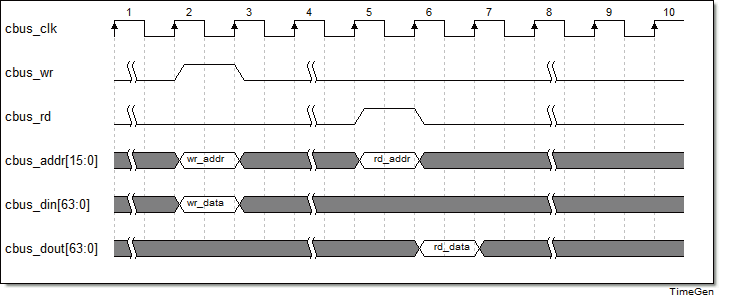

圖5

該模塊為AXI 轉CBUS 模塊。該模塊實現將來自PCIE IP 核的M_AXI 接口轉換成用戶讀寫寄存器CBUS接口。接口定義及時序如下。

cbus_addr: 寄存器地址。

cbus_wr: 寄存器寫使能。

cbus_rd: 寄存器讀使能。

cbus_din: 寄存器寫數據。

cbus_dout: 寄存器讀返回數據。

圖6 讀寫時序邏輯設計

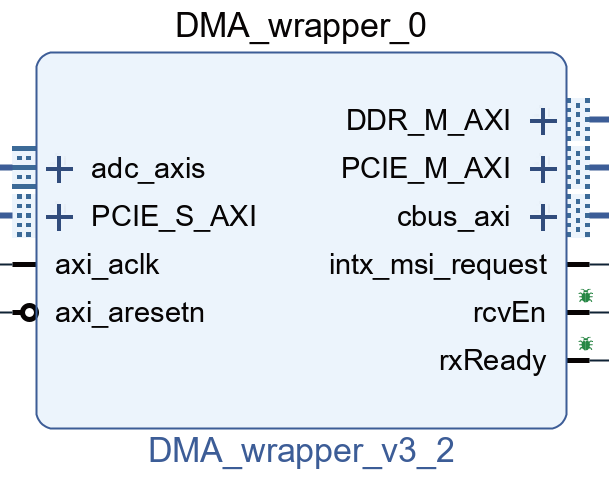

3.4 DMA收發控制器

圖7

該模塊為DMA 收發控制器模塊。該模塊實現上下行數據的DMA 傳輸。用戶上行數據通過adc_axis 接口寫入,通過PCIE_M_AXI 接口寫入AXI PCIE 橋。用戶下行的數據通過PCIE_M_AXI 接口從AXI PCIE 橋讀返回后,通過DDR_M_AXI 接口寫入FPGA 板載DDR4。PCIE_S_AXI 接口用于上位機通過AXI PCIE 橋來訪問DMA 收發控制器中的各個配置寄存器。cbus_axi 接口用于上位機通過AXI PCIE 橋來訪問用戶側的自定義寄存器。axi_aclk為AXI PCIE 橋產生的250 MHz 時鐘。Intx_msi_request為DMA 收發中斷。RcvEn 為上位機發出接收使能信號。Rxready 為DMA 接收控制器準備好信號。

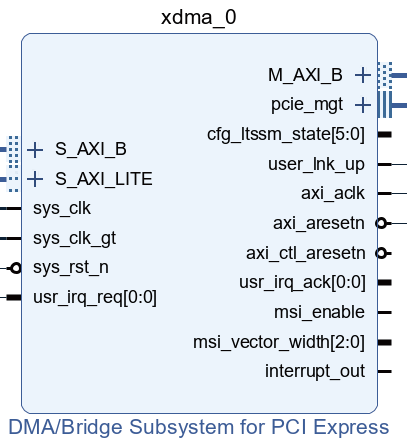

3.5 AXI PCIE橋模塊

圖8

該模塊為AXI PCIE 橋模塊。此模塊為XILINX 提供的IP 核,具體設置以及接口說明可參考官方手冊pg195 DMA/Bridge Subsystem for PCI Express v4.1。本設計中M_AXI_B 接口用于上位機讀寫DMA 收發控制器中的配置寄存器或者用戶側自定義的寄存器。S_AXI_B 接口用于DMA 收發控制器訪問上位機內存地址空間。S_AXI_LITE 接口用于動態配置AXI PCIE橋模塊,本設計不實際使用。Usr_irq_req 為DMA 收發控制器產生的中斷請求。PCIE_MGT 為8x Gen3 的PCIe 收發串行鏈路。s_axi_aclk 和s_axi_aresetn 為PCIe 輸出時鐘(250 M)和復位信號( 低有效)。其余輸入輸出接口本設計不實際使用。

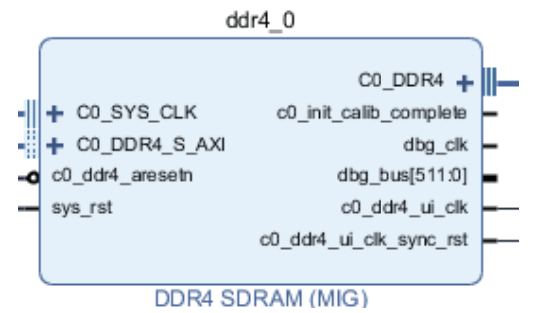

3.6 MIG模塊

圖9

該模塊為MIG 模塊,此模塊為XILINX 提供的IP 核,具體設置以及接口說明可參考官方手冊pg150 LogiCOREIP UltraScale Architecture-Based FPGAs Memory Interface Solutions v4.2。本設計中采用64 位DDR 數據位寬,時鐘1 200M。AXI 數據位寬512 位,輸入參考時鐘300M。

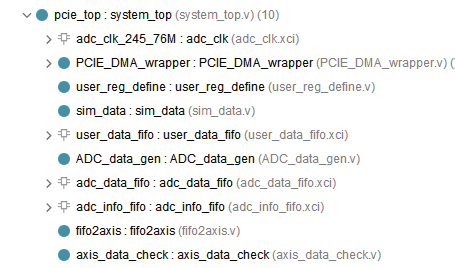

4 仿真與測試

采用Vivado2020.2 軟件進行本次開發設計工作,開發的FPGA 型號為XCZU27DR-ff vg1517-2-i,本次設計通過基帶板以及整個采集平臺,驗證本次試驗的可行性。

圖10

測試結果運行測試程序,啟動上行測試,上行測試結果如下圖所示,上行速率測試6 276 Mbyte/s,下行測試結果如下圖所示,下行速率測試6 620 Mbyte/s, 滿足數據實時傳輸要求。

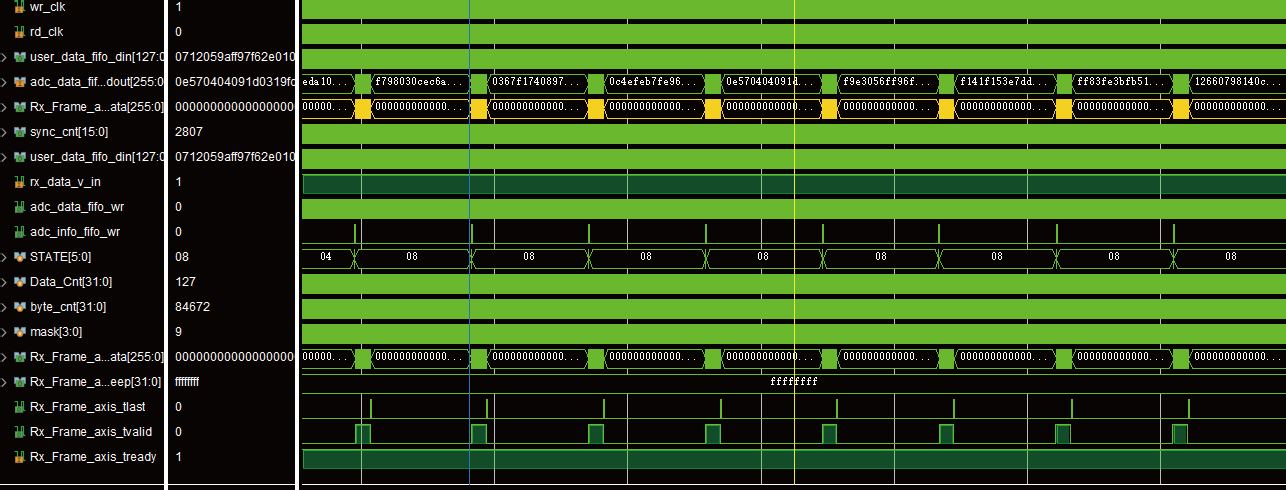

邏輯仿真(部分)

圖11

5 結束語

本研究完成了毫米波基帶數據的實時傳輸,本設計主要研究開發了,經過仿真和硬件驗證了傳輸的正確性,確認了本研究的可行性。

參考文獻:

[1] 袁行猛,徐蘭天,李奧.5G毫米波基帶數據傳輸的研究與實現[J].電子產品世界.2021(4):68-72.

[2] 何世文,黃永明, 王海明,等.毫米波無線通信發展趨勢及技術挑戰[J].電信科學.2017(6):11-19.

[3] 黃宇紅,劉盛綱,楊光,等.5G高頻系統關鍵技術及設計[M].北京:人民郵電出版社.2018.

[4] 3GPP TS 38.215:NR;Physical layer measurements[S].

[5] 3GPP TS 38.214:NR;Physical layer procedures for data[S].

(本文來源于《電子產品世界》雜志2023年5月期)

評論