EEPW首頁(yè) >>

主題列表 >>

fir ip

fir ip 文章 最新資訊

用DSP實(shí)現(xiàn)FIR數(shù)字濾波器

- FIR濾波器具有幅度特性可隨意設(shè)計(jì)、線性相位特性可嚴(yán)格精確保證等優(yōu)點(diǎn),因此在要求相位線性信道的現(xiàn)代電子系統(tǒng),如圖像處理、數(shù)據(jù)傳輸?shù)炔ㄐ蝹鬟f系統(tǒng)中,具有很大吸引力。本文簡(jiǎn)單介紹了其線性相位條件和設(shè)計(jì)方法,并且提供了一種用DSP實(shí)現(xiàn)的方法。 一、 引 言 在許多信息處理過(guò)程中,如對(duì)信號(hào)的過(guò)濾、檢測(cè)、預(yù)測(cè)等,都要廣泛地用到濾波器,而數(shù)字濾波器則因其設(shè)計(jì)靈活、實(shí)現(xiàn)方便等特點(diǎn)而廣為接受。 所謂數(shù)字濾波器就是具有某種選擇性的器件、網(wǎng)絡(luò)或以計(jì)算機(jī)硬件支持的計(jì)算程序。其功能本質(zhì)是按事先設(shè)計(jì)好的程序,

- 關(guān)鍵字: DSP FIR 數(shù)字濾波器

Matlab輔助DSP設(shè)計(jì)FIR數(shù)字濾波器

- l 引 言 隨著信息技術(shù)和計(jì)算機(jī)技術(shù)的飛速發(fā)展,數(shù)字信號(hào)處理技術(shù)在眾多領(lǐng)域得到廣泛應(yīng)用。數(shù)字濾波器由于其精度高、穩(wěn)定性好、使用靈活等優(yōu)點(diǎn),廣泛應(yīng)用在各種數(shù)字信號(hào)處理領(lǐng)域。數(shù)字濾波器根據(jù)沖擊響應(yīng)函數(shù)的時(shí)域特性,可以分為FIR(有限長(zhǎng)沖擊響應(yīng)濾波器)和IIR(無(wú)限長(zhǎng)沖擊響應(yīng)濾波器)。FIR濾波器與IIR濾波器相比,具有嚴(yán)格的線性相位,幅度特性可任意等優(yōu)點(diǎn)。而且,F(xiàn)IR濾波器的單位抽樣響應(yīng)是有限長(zhǎng)的,故一定是穩(wěn)定的,他又可以用快速傅里葉變換(FFT)算法來(lái)實(shí)現(xiàn)過(guò)濾信號(hào),可大大提高運(yùn)算效率。 Ma

- 關(guān)鍵字: Matlab DSP FIR 數(shù)字濾波器

基于IP核的FIR低通濾波器的設(shè)計(jì)與實(shí)現(xiàn)

- 0.引言 FIR(Finite Impulse Response,有限沖擊響應(yīng))數(shù)字濾波器具有穩(wěn)定性高、可以實(shí)現(xiàn)線性相位等優(yōu)點(diǎn),廣泛被應(yīng)用于信號(hào)檢測(cè)與處理等領(lǐng)域[1,2]。由于FPGA(Field Programmable Gate Array,現(xiàn)場(chǎng)可編程門陣列)基于查找表的結(jié)構(gòu)和全硬件并行執(zhí)行的特性,如何用FPGA 來(lái)實(shí)現(xiàn)高速FIR 數(shù)字濾波器成了近年來(lái)數(shù)字信號(hào)處理領(lǐng)域研究的熱點(diǎn)。目前,全球兩大PLD 器件供應(yīng)商都提供了加速FPGA 開發(fā)的IP(IntelligentProperty,知識(shí)產(chǎn)權(quán)

- 關(guān)鍵字: IP核 FIR 低通濾波器

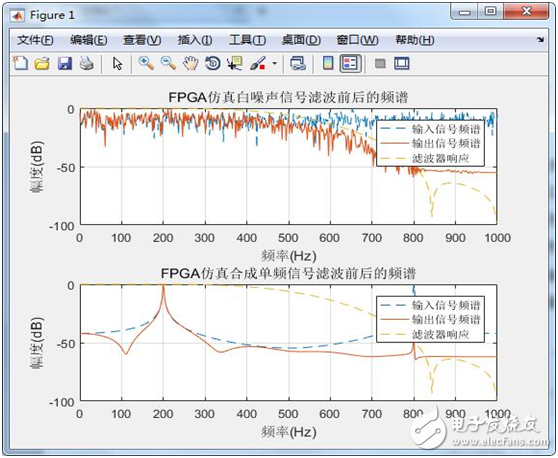

基于FPGA的FIR數(shù)字濾波器設(shè)計(jì)與仿真

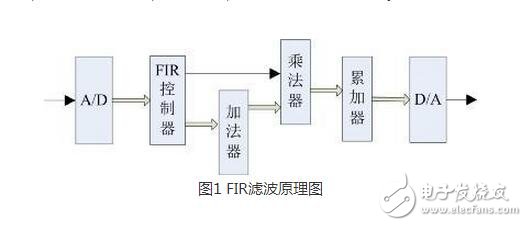

- 實(shí)現(xiàn)數(shù)字化是控制系統(tǒng)的重要發(fā)展方向,而數(shù)字信號(hào)處理已在通信、語(yǔ)音、圖像、自動(dòng)控制、雷達(dá)、軍事、航空航天等領(lǐng)域廣泛應(yīng)用。數(shù)字信號(hào)處理方法通常涉及變換、濾波、頻譜分析、編碼解碼等處理。數(shù)字濾波是重要環(huán)節(jié),它能滿足濾波器對(duì)幅度和相位特性的嚴(yán)格要求,克服模擬濾波器所無(wú)法解決的電壓和溫度漂移以及噪聲等問題。而有限沖激響應(yīng)FIR濾波器在設(shè)計(jì)任意幅頻特性的同時(shí)能夠保證嚴(yán)格的線性相位特性。利用FPGA可以重復(fù)配置高精度的FIR濾波器,使用VHDL硬件描述語(yǔ)言改變?yōu)V波器的系數(shù)和階數(shù),并能實(shí)現(xiàn)大量的卷積運(yùn)算算法。結(jié)合MA

- 關(guān)鍵字: FPGA FIR 數(shù)字濾波器

基于FPGA 的FIR 數(shù)字濾波器設(shè)計(jì)方案

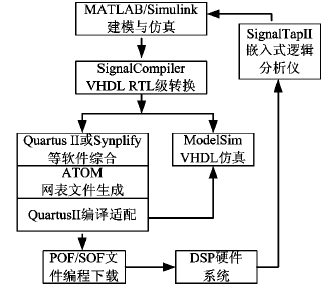

- 本文簡(jiǎn)要介紹了FIR數(shù)字濾波器的結(jié)構(gòu)特點(diǎn)和基本原理,提出基于FPGA和DSP Builder的FIR數(shù)字濾波器的基本設(shè)計(jì)流程和實(shí)現(xiàn)方案。 在Matlab/Simulink環(huán)境下,采用DSP Builder模塊搭建FIR模型,根據(jù)FDATool工具對(duì)FIR濾波器進(jìn)行了設(shè)計(jì),然后進(jìn)行系統(tǒng)級(jí)仿真和ModelSim功能仿真,其仿真結(jié)果表明其數(shù)字濾波器的濾波效果良好。通過(guò)SignalCompiler把模型轉(zhuǎn)換成VHDL語(yǔ)言加入到FPGA的硬件設(shè)計(jì)中,從QuartusⅡ軟件中的虛擬邏輯分析工具SignalT

- 關(guān)鍵字: FPGA FIR 數(shù)字濾波器

基于VerilogHDL的FIR數(shù)字濾波器設(shè)計(jì)與仿真

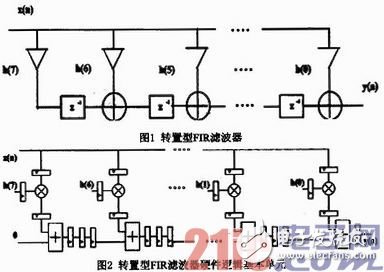

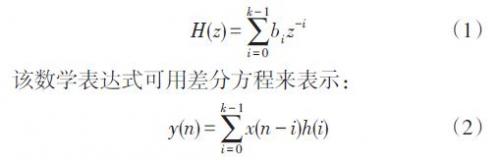

- 引言 數(shù)字濾波器是語(yǔ)音與圖像處理、模式識(shí)別、雷達(dá)信號(hào)處理、頻譜分析等應(yīng)用中的一種基本的處理部件, 它能滿足波器對(duì)幅度和相位特性的嚴(yán)格要求, 避免模擬濾波器所無(wú)法克服的電壓漂移、溫度漂移和噪聲等問題。有限沖激響應(yīng)(FIR)濾波器能在設(shè)計(jì)任意幅頻特性的同時(shí)保證嚴(yán)格的線性相位特性。 1 FIR 數(shù)字濾波器 FIR 濾波器用當(dāng)前和過(guò)去輸入樣值的加權(quán)和來(lái)形成它的輸出, 如下所示的前饋差分方程所描述的。 FIR 濾波器又稱為移動(dòng)均值濾波器, 因?yàn)槿魏螘r(shí)間點(diǎn)的輸出

- 關(guān)鍵字: Verilog FIR 數(shù)字濾波器

簡(jiǎn)單實(shí)用的路由器經(jīng)典設(shè)計(jì)匯總

- 路由器(Router),是連接因特網(wǎng)中各局域網(wǎng)、廣域網(wǎng)的設(shè)備,它會(huì)根據(jù)信道的情況自動(dòng)選擇和設(shè)定路由,以最佳路徑,按前后順序發(fā)送信號(hào)。 路由器是互聯(lián)網(wǎng)絡(luò)的樞紐,"交通警察"。目前路由器已經(jīng)廣泛應(yīng)用于各行各業(yè),各種不同檔次的產(chǎn)品已成為實(shí)現(xiàn)各種骨干網(wǎng)內(nèi)部連接、骨干網(wǎng)間互聯(lián)和骨干網(wǎng)與互聯(lián)網(wǎng)互聯(lián)互通業(yè)務(wù)的主力軍。本文專門介紹基于各種架構(gòu)路由器的設(shè)計(jì)方案,供大家參考。 嵌入式Linux的SOHO路由器電路設(shè)計(jì) 針對(duì)目前SOHO路由器設(shè)計(jì)方案難以滿足高速接入網(wǎng)用戶要求和存在系統(tǒng)穩(wěn)定性

- 關(guān)鍵字: IP VPDN

Mentor Graphics宣布推出新的用于PCIe 4.0的驗(yàn)證IP

- Mentor Graphics公司今天宣布其新的Mentor®EZ-VIP PCI Express驗(yàn)證IP的即時(shí)可用性。這一新的驗(yàn)證IP (VIP)可將ASIC(應(yīng)用程序特定集成電路)和FPGA(現(xiàn)場(chǎng)可編程門陣列)設(shè)計(jì)驗(yàn)證的測(cè)試平臺(tái)構(gòu)建時(shí)間減少多達(dá)10倍。 驗(yàn)證IP旨在通過(guò)為常見協(xié)議和架構(gòu)提供可復(fù)用構(gòu)建模塊來(lái)幫助工程師減少構(gòu)建測(cè)試平臺(tái)所花費(fèi)的時(shí)間。然而,即使是標(biāo)準(zhǔn)協(xié)議和常見架構(gòu),其配置和實(shí)施也可能會(huì)因設(shè)計(jì)而異。因此,傳統(tǒng)的VIP元件可能需要數(shù)天甚至數(shù)周來(lái)準(zhǔn)備模擬或仿真測(cè)試平臺(tái)。 &

- 關(guān)鍵字: Mentor Graphics IP SoC

新思科技Synopsys虛擬原型設(shè)計(jì)專著發(fā)行超3000本,讀者覆蓋超1000家公司

- 為加速芯片和電子系統(tǒng)創(chuàng)新而提供軟件、知識(shí)產(chǎn)權(quán)(IP)及服務(wù)的全球性領(lǐng)先供應(yīng)商新思科技公司(Synopsys, Inc.)日前宣布:其關(guān)于虛擬原型技術(shù)的專著《更快地開發(fā)出更好的軟件!(Better Software. Faster!)》已實(shí)現(xiàn)超過(guò)3000本的發(fā)行量,覆蓋了1000多家公司。此書的廣泛發(fā)行表明:業(yè)界正日漸把虛擬原型設(shè)計(jì)看作是一種可幫助他們?cè)谠O(shè)計(jì)周期的更早階段就開始軟件開發(fā)并加速其項(xiàng)目進(jìn)度的方法。Synopsys已將此書翻譯為簡(jiǎn)體中文,日文版將于今年年底前提供。 “隨著移動(dòng)

- 關(guān)鍵字: 新思科技 IP

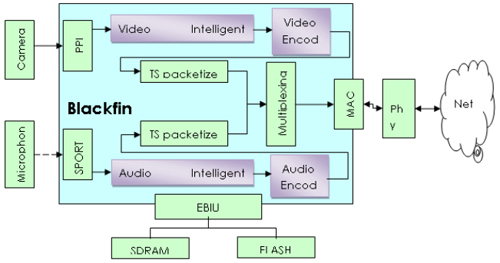

基于Blackfin的智能IP Camera系統(tǒng)設(shè)計(jì)

- 1.背景及概述 近年來(lái),隨著嵌入式應(yīng)用越來(lái)越復(fù)雜,應(yīng)用場(chǎng)合越來(lái)越多,特別是多媒體功能在各個(gè)領(lǐng)域飛速發(fā)展,高性能計(jì)算變得無(wú)處不在,從消費(fèi)電子,網(wǎng)絡(luò)通訊到工業(yè)控制和監(jiān)控,大多數(shù)應(yīng)用都需要更高的數(shù)字信號(hào)處理能力。出于成本和設(shè)計(jì)難度的考慮,人們傾向于使用單顆芯片完成所有的工作,傳統(tǒng)的DSP處理器和MCU處理器開始以多種形式進(jìn)行融合: 1.傳統(tǒng)的MCU+DSP合作方案被集成到一顆芯片封裝內(nèi);或者進(jìn)一步實(shí)現(xiàn)為真正的異構(gòu)多核,可以共享部分甚至全部外部設(shè)備。 2.以SoC的形式為MCU加上基于固定硬

- 關(guān)鍵字: Blackfin IP Camera DSP

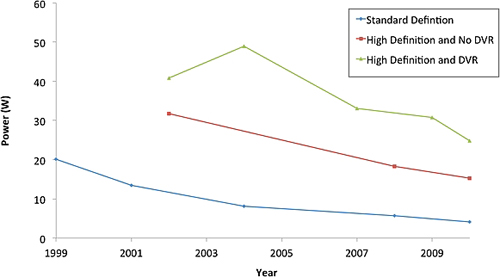

機(jī)頂盒與節(jié)能

- 每年年初,我家都會(huì)盡量省著點(diǎn)用錢。一般都以相同的方式開始:非常嚴(yán)格,甚至有些苛刻。我們下飯館的次數(shù)比往常有所減少,用電更節(jié)約,而且上班帶飯?jiān)谵k公室吃。我妻子是我們家的首席財(cái)務(wù)官,因此她會(huì)準(zhǔn)備一個(gè)節(jié)約事項(xiàng)清單。無(wú)論好壞,短期內(nèi)我們都不能大手大腳地花錢,得回歸過(guò)去的老習(xí)慣。 不過(guò)今年情況有了變化。我們有一部 13 年前安裝的座機(jī)電話。我們每月都付電話費(fèi),但服務(wù)質(zhì)量從未改善,而且也未曾降價(jià)。于是我們決定試試 IP 電話。通過(guò)停用座機(jī)電話,再加上有線電視供應(yīng)商提供的優(yōu)惠,我們每月可節(jié)省大約 100 美元。節(jié)

- 關(guān)鍵字: IP 電話 有線電視盒 電源管理策略

華虹宏力攜手硅視覺,在其0.11微米技術(shù)平臺(tái)上共推硅驗(yàn)證智能藍(lán)牙射頻IP

- 世界領(lǐng)先的8英寸純晶圓代工廠之一,上海華虹宏力半導(dǎo)體制造有限公司(以下簡(jiǎn)稱“華虹宏力”),與硅視覺技術(shù)有限公司(以下簡(jiǎn)稱“硅視覺”),一家領(lǐng)先的知識(shí)產(chǎn)權(quán)(IP)提供商,提供高性能、低功率射頻知識(shí)產(chǎn)權(quán),今天宣布攜手合作,在華虹宏力0.11微米混合信號(hào)/射頻技術(shù)平臺(tái)上推出了藍(lán)牙低功耗IP。這款通過(guò)硅驗(yàn)證的IP已被授權(quán)給一家客戶,該客戶應(yīng)用藍(lán)牙技術(shù)開發(fā)了無(wú)線鍵盤鼠標(biāo)等人機(jī)接口設(shè)備。為滿足集成藍(lán)牙模塊的無(wú)線MCU需求,接下來(lái)將很快在華虹宏力射頻嵌入式非易失性存儲(chǔ)

- 關(guān)鍵字: 華虹 宏力 射頻 IP

Synopsys發(fā)布業(yè)界首款完整的PCI Express 4.0 IP解決方案

- 為加速芯片和電子系統(tǒng)創(chuàng)新而提供軟件、知識(shí)產(chǎn)權(quán)(IP)及服務(wù)的全球性領(lǐng)先供應(yīng)商新思科技公司(Synopsys, Inc.,納斯達(dá)克股票市場(chǎng)代碼:SNPS)日前發(fā)布了業(yè)界首款完整的PCI Express 4.0 IP解決方案,它由DesignWare PHY、控制器和Verification IP(VIP)組成,專門針對(duì)諸如服務(wù)器、網(wǎng)絡(luò)設(shè)備、存儲(chǔ)系統(tǒng)以及固態(tài)硬盤(SSD)等企業(yè)級(jí)計(jì)算應(yīng)用。PCI Express 4.0是PCI Express I/O的下一代標(biāo)準(zhǔn),其吞吐量增加了一倍至16 GT/s,目前外

- 關(guān)鍵字: Synopsys PCI Express IP

Altera與Cavium合作,為網(wǎng)絡(luò)應(yīng)用提供經(jīng)過(guò)預(yù)驗(yàn)證的數(shù)據(jù)包分類解決方案

- Altera公司(NASDAQ: ALTR)近日宣布,其Interlaken旁視知識(shí)產(chǎn)權(quán)(IP)內(nèi)核通過(guò)了測(cè)試,與Cavium的NEURON Search?處理器兼容。 這一可立即部署實(shí)施、經(jīng)過(guò)預(yù)先驗(yàn)證的解決方案為網(wǎng)絡(luò)OEM提供了低延時(shí)、高性能數(shù)據(jù)包接口,適用于包括路由器、交換機(jī)、防火墻以及安全存儲(chǔ)在內(nèi)的多種網(wǎng)絡(luò)應(yīng)用。Interlaken旁視IP內(nèi)核目前以Altera系列同類最佳IP內(nèi)核組成的形式提供,經(jīng)過(guò)優(yōu)化,集成在Altera Arria? 10和Stratix? V FPGA中,具有性能優(yōu)異、

- 關(guān)鍵字: Altera IP Cavium

Synopsys發(fā)起的“IP Accelerated”計(jì)劃重新定義了IP供應(yīng)商范式

- 為加速芯片和電子系統(tǒng)創(chuàng)新而提供軟件、知識(shí)產(chǎn)權(quán)(IP)及服務(wù)的全球性領(lǐng)先供應(yīng)商新思科技公司(Synopsys, Inc.,納斯達(dá)克股票市場(chǎng)代碼:SNPS)日前宣布:推出其名為“IP Accelerated”的IP加速計(jì)劃,以幫助設(shè)計(jì)師顯著地減少在其系統(tǒng)級(jí)芯片(SoC)中集成IP所需的時(shí)間和工作量。該計(jì)劃擴(kuò)展了Synopsys已有的、多樣化的、已流片驗(yàn)證過(guò)的DesignWare? IP產(chǎn)品組合,增加了全新的IP Prototyping Kits原型設(shè)計(jì)套件、IP Virtual Development K

- 關(guān)鍵字: Synopsys IP SoC

fir ip介紹

您好,目前還沒有人創(chuàng)建詞條fir ip!

歡迎您創(chuàng)建該詞條,闡述對(duì)fir ip的理解,并與今后在此搜索fir ip的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fir ip的理解,并與今后在此搜索fir ip的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司