fifo 文章 最新資訊

多路數(shù)據(jù)采集系統(tǒng)中FIFo的設(shè)計

- 摘 要:首先介紹了多路數(shù)據(jù)采集系統(tǒng)的總體設(shè)計、FIFO芯片IDT7202。然后分別分析了FIFO與CPLD、AD接口的設(shè)計方法。由16位模數(shù)轉(zhuǎn)換芯片AD976完成模擬量至位數(shù)字量的轉(zhuǎn)換,由ATERA公司的可編程邏輯器件EPM7256A完成對數(shù)

- 關(guān)鍵字: FIFo 多路數(shù)據(jù)采集 系統(tǒng)

基于FPGA的多路數(shù)字量采集模塊設(shè)計

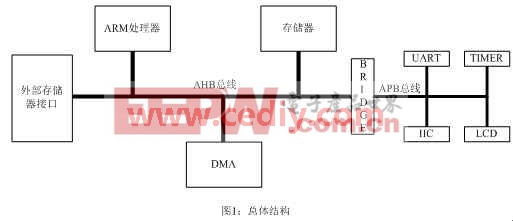

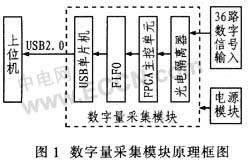

- 1 引言 測控系統(tǒng)常常需要處理所采集到的各種數(shù)字量信號。通常測控系統(tǒng)采用通用MCU完成系統(tǒng)任務。但當系統(tǒng)中采集信號量較多時,僅依靠MCU則難以完成系統(tǒng)任務。針對這一問題,提出一種基于FPGA技術(shù)的多路數(shù)字量采集模塊。利用FPGA的I/O端口數(shù)多且可編程設(shè)置的特點,配以VHDL編寫的FPGA內(nèi)部邏輯,實現(xiàn)采集多路數(shù)字量信號。 2 模塊設(shè)計方案 2.1 功能要求 該數(shù)字量采集模塊主要功能是采集輸入的36路數(shù)字及脈沖信號,并將編幀后的信號數(shù)據(jù)上傳給上位機,上位機經(jīng)解包處理后顯示信號相

- 關(guān)鍵字: FPGA 數(shù)字量采集 測控 USB單片機 MCU FIFO

基于短時能量和短時過零率的VAD算法及其FPGA實現(xiàn)

- 語音激活檢測VAD(Voice Activity Detection)是一種通過特定的判決準則判斷語音中出現(xiàn)的停頓和靜默間隔,檢測出有效語音部分的技術(shù)。運用這種技術(shù)可以在確保語音質(zhì)量的前提下,對不同類別的語音段采用不同的比特數(shù)進行編碼,從而降低語音的編碼速率。由于在雙工移動通信系統(tǒng)中,一方只有35%的時間處于激活狀態(tài)[1],如何降低靜音期的編碼速率對于減少傳輸帶寬、功率以及容量具有積極的作用,因此VAD技術(shù)在語音通信領(lǐng)域具有重要的使用價值。隨著適合于變比特率語音編碼的CDMA和PRMA等多址技術(shù)的出現(xiàn)

- 關(guān)鍵字: FPGA VAD 短時能量 短時過零率 FIFO 濾波器

高速數(shù)據(jù)采集系統(tǒng)中的存儲與傳輸控制邏輯設(shè)計

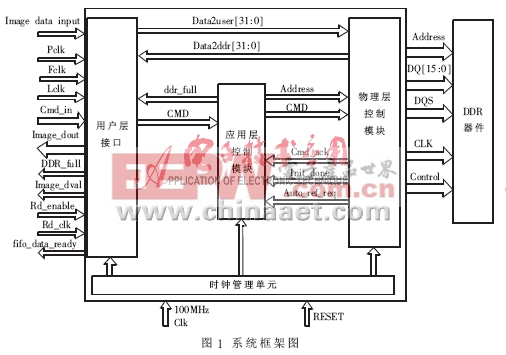

- 隨著信息科學的飛速發(fā)展,數(shù)據(jù)采集和存儲技術(shù)廣泛應用于雷達、通信、遙測遙感等領(lǐng)域。在高速數(shù)據(jù)采集系統(tǒng)中,由ADC轉(zhuǎn)換后的數(shù)據(jù)需要存儲在存儲器 中,再進行相應的處理,保證快速準確的數(shù)據(jù)傳輸處理是實現(xiàn)高速數(shù)據(jù)采集的一個關(guān)鍵。由于高速ADC的轉(zhuǎn)換率很高,而大容量RAM相對ADC輸出速度較慢, 保持高速數(shù)據(jù)存儲過程的可靠性、實時性是一個比較棘手的問題。對于數(shù)據(jù)采集系統(tǒng)中的大容量高速度數(shù)據(jù)存儲、傳輸,本文提出一種基于FPGA的多片RAM實 現(xiàn)高速數(shù)據(jù)的存儲和傳輸?shù)姆桨福糜?GS/s數(shù)據(jù)采集系統(tǒng)中,實現(xiàn)了以低

- 關(guān)鍵字: 數(shù)據(jù)采集 存儲 傳輸 ADC SRAM RAM FIFO

基于Verilog HDL的異步FIFO設(shè)計與實現(xiàn)

- 在現(xiàn)代IC設(shè)計中,特別是在模塊與外圍芯片的通信設(shè)計中,多時鐘域的情況不可避免。當數(shù)據(jù)從一個時鐘域傳遞到另一個域,并且目標時鐘域與源時鐘域不相關(guān)時,這些域中的動作是不相關(guān)的,從而消除了同步操作的可能性,并使系統(tǒng)重復地進入亞穩(wěn)定狀態(tài)[1]。在有大量的數(shù)據(jù)需要進行跨時鐘域傳輸且對數(shù)據(jù)傳輸速度要求比較高的場合,異步FIFO是一種簡單、快捷的解決方案。 異步FIFO用一種時鐘寫入數(shù)據(jù),而用另外一種時鐘讀出數(shù)據(jù)。讀寫指針的變化動作由不同的時鐘產(chǎn)生。因此,對FIFO空或滿的判斷是跨時鐘域的。如何根據(jù)異步的指針

- 關(guān)鍵字: FIFO 異步 Verilog HDL IC 亞穩(wěn)態(tài)

fifo介紹

采用FIFO方式時,信息被以所收到的次序進行傳輸。

表示信息存儲的一種數(shù)據(jù)結(jié)構(gòu),含義是先進入的對象先取出。隊列(Queue )就是基于這種性質(zhì)實現(xiàn)的。

FIFO( First In First Out)簡單說就是指先進先出。由于微電子技術(shù)的飛速發(fā)展,新一代FIFO芯片容量越來越大,體積越來越小,價格越來越便宜。作為一種新型大規(guī)模集成電路,F(xiàn)IFO芯片以其靈活、方便、高效的特性,逐漸在高速數(shù)據(jù)采 [ 查看詳細 ]

相關(guān)主題

關(guān)于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司