- 不管是放到測試設置中,還是作為被測設備的一部分,時鐘恢復都在進行準確的測試測量時發揮著重要作用。由于大多數千兆位通信系統都是同步系統,因此系統內部的數據都使用公共時鐘定時。不管是沿著幾英寸的電路板傳送

- 關鍵字:

PLL 時鐘恢復 設計方案

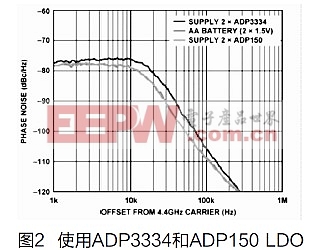

- 摘要:鎖相環是現代通信系統的基本構建模塊,而電源噪聲越來越影響鎖相環性能。本文通過列舉多種電源管理電路設計的新方法,解析不同的設計對鎖相環性能產生的影響。

- 關鍵字:

VCO PLL 201209

- 摘要:本設計基于DDS原理和FPGA技術按照順序存儲方式,將對正弦波、方波、三角波、鋸齒波四種波形的取樣數據依次全部存儲在ROM波形表里,通過外接設備撥扭開關和鍵盤控制所需波形信號的輸出,最終將波形信息顯示在LC

- 關鍵字:

FPGA DDS 信號發生器

- 1引言高性能合成頻率廣泛應用在現代通信、雷達和電子測量等技術領域中。頻率合成方法主要有3種...

- 關鍵字:

DDS PLL技術 高頻時鐘

- 1971年3月,美國學者J.Tierncy,C.M.Rader和B.Gold最先提出直接數字合成技術(DirectDigitalSynthesis),簡稱D...

- 關鍵字:

DDS 任意波形發生器 頻率合成

- DDS同 DSP(數字信號處理)一樣,是一項關鍵的數字化技術。DDS是直接數字式頻率合成器(Direct Digital Synthesizer)的英文縮寫。與傳統的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉換時間等優點,廣

- 關鍵字:

FPGA DDS 原理

- 在非相參雷達測試系統中,頻率合成技術是其中的關鍵技術之一,它要求在一個很寬的頻率范圍內以快捷的速度,提供大...

- 關鍵字:

PLL 低相位噪聲 環路濾波器

- 一般情況下,可以用一個現有的振蕩器,為一個UART產生一個波特率時鐘。振蕩器頻率必須作分頻,而分頻會帶來波...

- 關鍵字:

DDS 波特率發生器 示波器

- XC25BS7系列是內置分頻,倍頻電路,在整個頻率范圍內保持低消耗電流,具有超小型封裝的PLL時鐘發生器IC。輸...

- 關鍵字:

PLL 時鐘發生器 XC25BS7

- 摘要:定時同步是高速數據傳輸的關鍵技術也是難點問題。在對鎖相環數字化設計、DDS原理結構和參數設計進行研究的基礎上,提出了一種基于DDS的高速定時同步方法,對該定時同步方法的原理結構框圖進行了詳細的論述,對

- 關鍵字:

同步 方法 定時 高速 DDS 基于

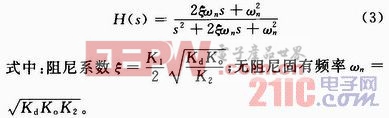

- 1 引言 本文在傳統鎖相環結構的基礎上進行改進,設計了一款用于多路輸出時鐘緩沖器中的鎖相環,其主 要結構包括分頻器、鑒頻鑒相器(PFD)、電荷泵、環路濾波器和壓控振蕩器(VCO)。在鑒相器前采用預 分頻結構減小時

- 關鍵字:

CSMC PLL 工藝 零延時

- 新款ADF4159上的鑒頻鑒相器最高工作頻率可達110MHz,功耗低于100mW;內置高分辨率25位小數N分頻模數和片內FMCW斜坡發生功能

全球領先的高性能信號處理解決方案供應商ADI最近推出業界性能最高的ADF415913GHzPLL頻率合成器。ADF4159實現了突破性的110MHz鑒頻鑒相器工作頻率,同時功耗低于100mW,僅為競爭解決方案的五分之一。此外,ADF4159包含25位固定模數和產生高線性斜坡曲線的片內功能,使其非常適合頻率調制連續波(FMCW)雷達應用,包括汽車雷達系統、微

- 關鍵字:

ADI 頻率合成器 PLL

dds+pll介紹

您好,目前還沒有人創建詞條dds+pll!

歡迎您創建該詞條,闡述對dds+pll的理解,并與今后在此搜索dds+pll的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473